![]() 記事作成中 Under construction

記事作成中 Under construction

サブプロジェクトについて

はじめに

本サブプロジェクトは、バッファ・アンプ回路を設計・製作します。電圧利得1・無帰還の回路です。

本プリント基板は部品として各プロジェクトで利用します。

プリント基板のガーバーデータ、部品表などの製造資料等については

「設計データ頒布」に記載しています。

背景・目的

ハイブリッドIC ( SATRI-IC )を使用する SATRI V4回路 では、入力する電圧信号を電流信号に変換する必要があります。 バッファアンプを使うことでどのような音の入力ソース(機器)にも対応できるよう入力インピーダンス設定抵抗を大きくとる事ができ、 かつ、ハイブリッドICに供給する電流信号も大きくすることができます。 これらは低雑音化による音質向上につながります。 (※使い方として、電圧電流変換抵抗(VI抵抗)を小さくして信号電流を大きくすることも可能となる)

以前であれば入力バッファには定番の 東芝製の 低雑音JFET である 2SJ74 / 2SK170 コンプリメンタリペアの

ソースフォロア回路にて手軽に高音質にすることが出来ました。

現状は国内メーカー半導体の JFETスルーホール品 はほぼ無くなってしまい、

表面実装でも コンプリ品種 は皆無なうえ更にPch品種自体もかなり少なく、

僅かにある品種も市場在庫ではIdssランクが揃わない状況だと認識しています。

となると海外製品の表面実装タイプでなんとか構成する必要があります。

表面実装部品では作るのが大変という印象もあるかもしれませんが、

小さな部品を最短距離で高密度実装することができます。

(スルーホール品の)リードが無い分、寄生インダクタンス・抵抗成分を比較的抑える事ができ、

設計次第では周波数特性向上あるいは安定度向上の可能性もありそうです。

本サブプロジェクトでは、より 高精度・低雑音なバッファ部品 を作ることを目的とします。

HBFBCについて

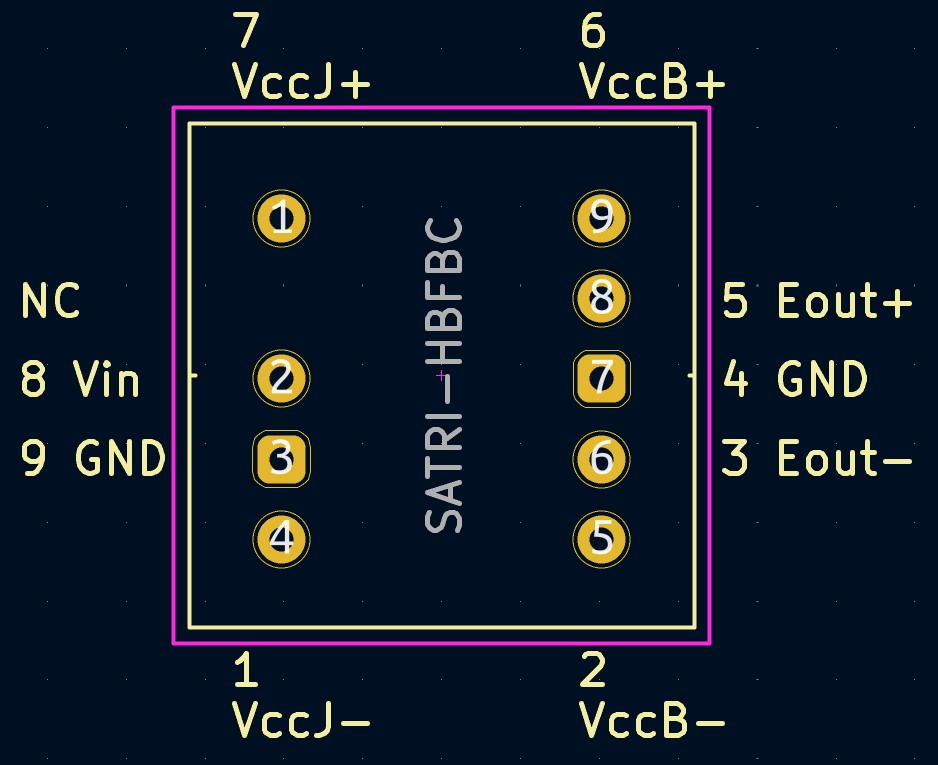

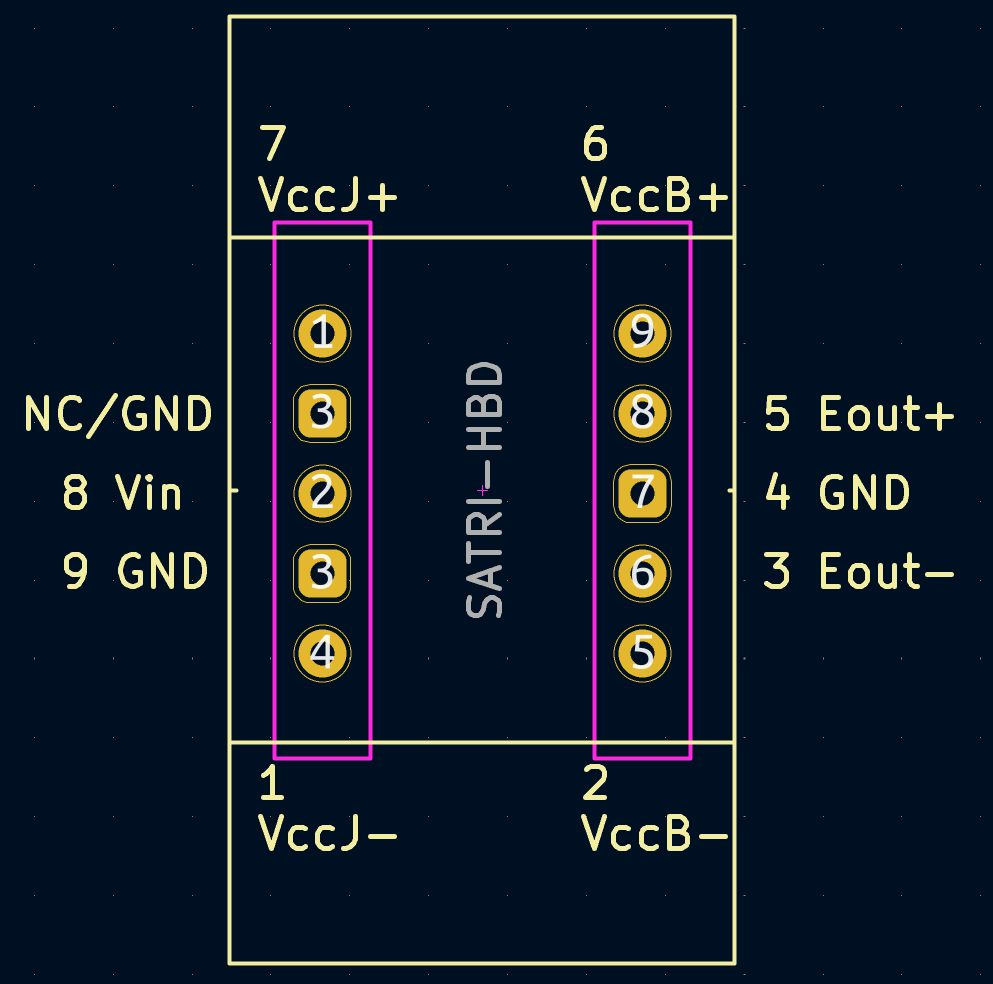

本サブプロジェクトのバッファ回路は、バクーンプロダクツ社のバッファIC「HBFBC」のピン配置を想定しています。

HBFBC は、HyBrid FET input Buffer Circuit の略とのこと。

スルーホール低雑音コンプリメンタリJFET の枯渇への対処、信号精度向上など複数の目的を満たすために設計されたと想像しています。

この JFET+BJT ですが、「続トランジスタ回路の設計(CQ出版)」の

混成ダーリントン(異種ダーリントン) という回路例で個人的に見覚えがありました。

留意点

- 工具については、別ページ「工具について」にまとめました。

- バッファ単体では信号増幅はしません。これ単体でプリアンプやヘッドホンアンプを作るのは推奨しません。

- 使用するJFETについては現行品の表面実装コンプリメンタリ品を見つけられず、 海外半導体メーカーのPch・Nch品を組み合わせて利用することになります。 なおBJTについては東芝など複数メーカーにて現行品コンプリメンタリペアがあるのでそれらを利用可能です。

コンポーネント:HBC (JFET-BJT バッファ基板 v1)

概要

『 HBC 』はバッファ基板です。プリアンプ基板にて必要となる部品です。

作業時期は、設計着手 2022年10月 、音出し 2022年12月 です。

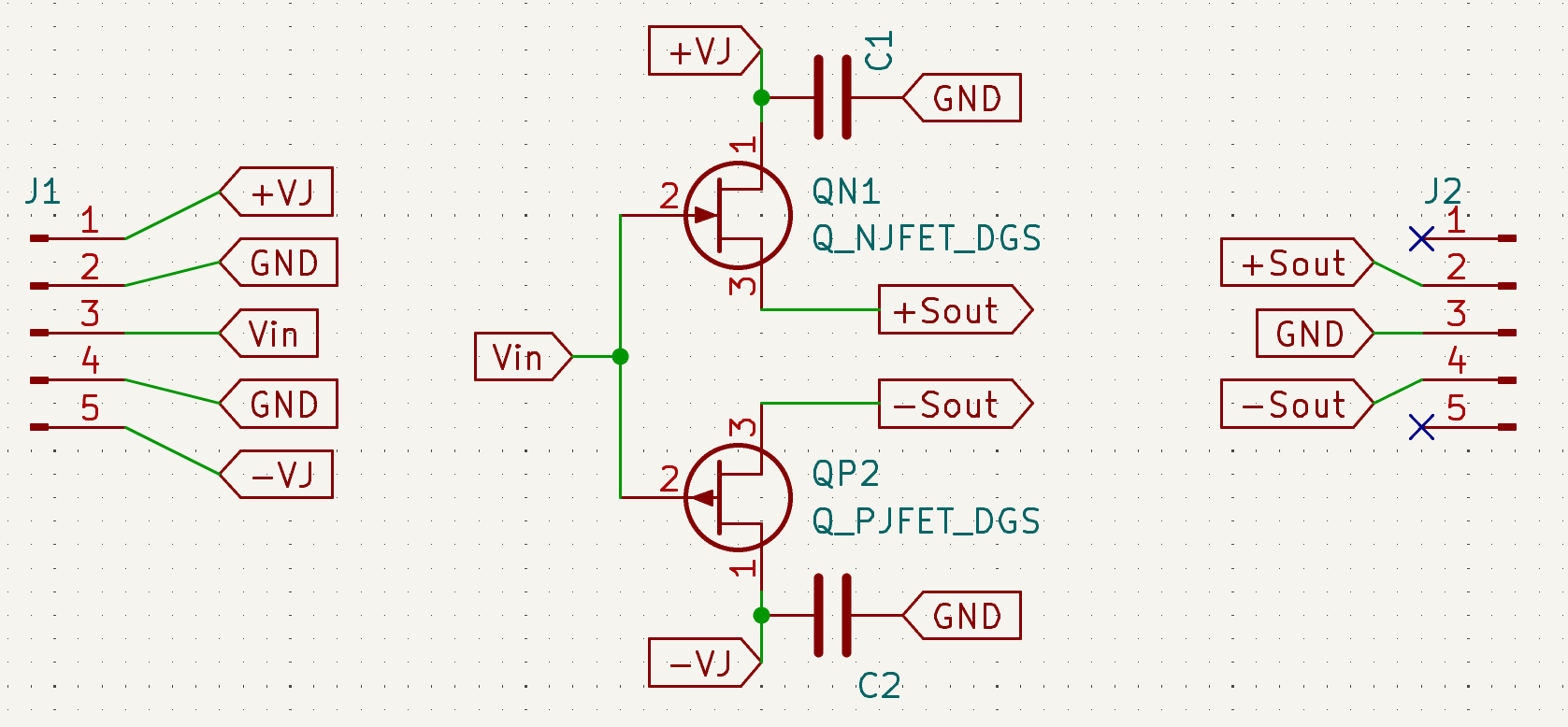

JFET入力・BJT出力 ということで「異種=ハイブリッド」なバッファ回路となっています。

HBFBCピン配置(フットプリント互換)、半導体回路の構成も恐らく踏襲しています。

本家のHBFBCは4個のトランジスタ(シングル2個、デュアル1個)のようです。

CQ出版社「続トランジスタ回路の設計」の混成ダーリントンあたりを回路想定して LTspice 回路シミュレーションで色々確認すると、

コンプリメンタリ JFETソースフォロア よりも良い結果が得られたことからそのまま基板作成することとしました。

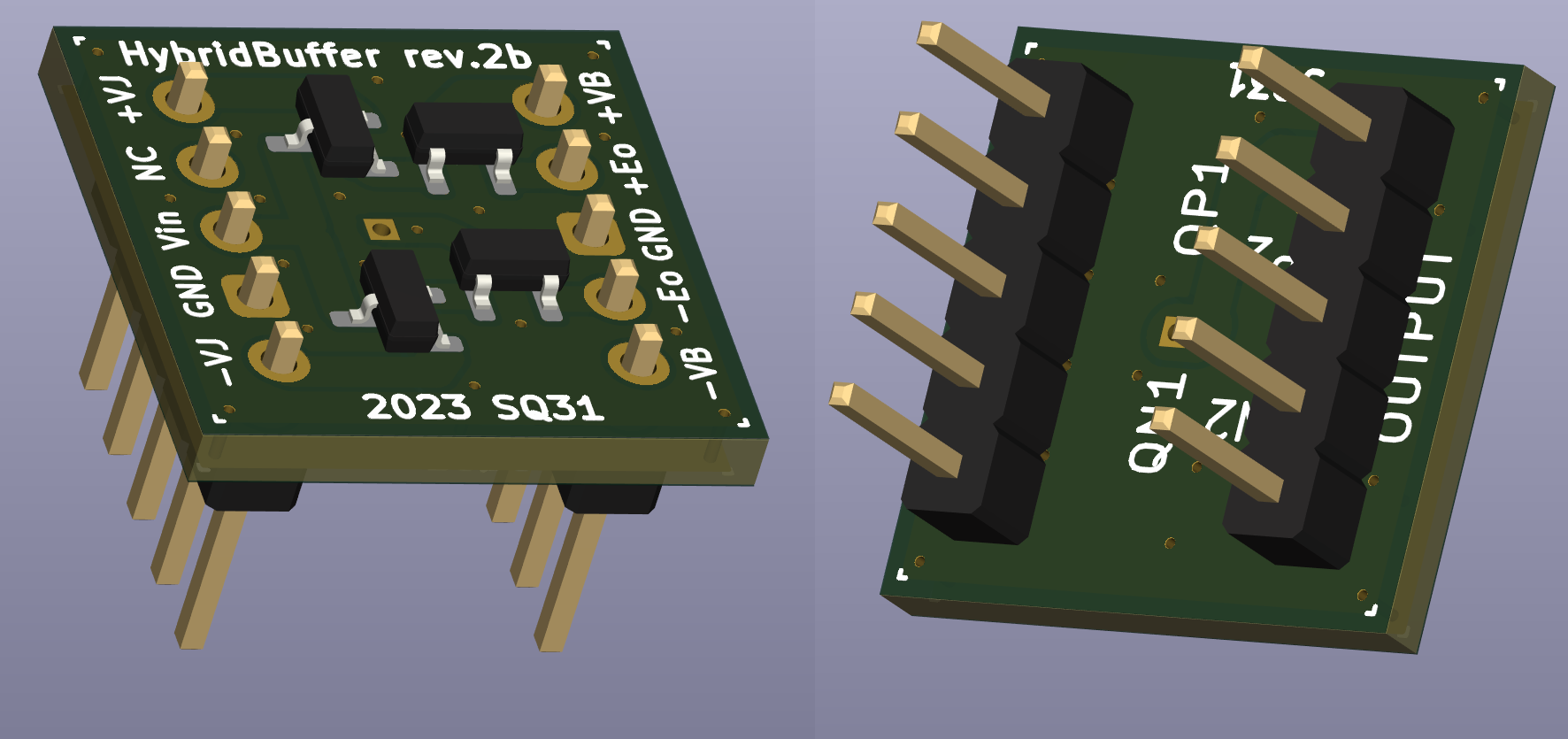

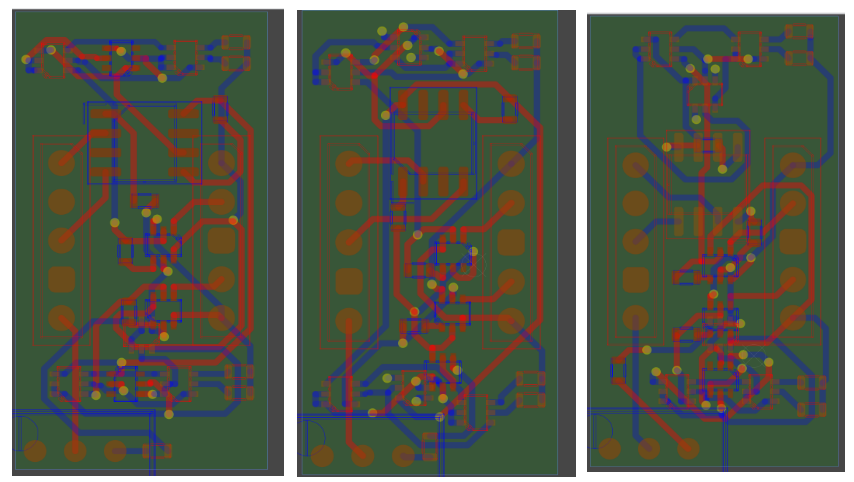

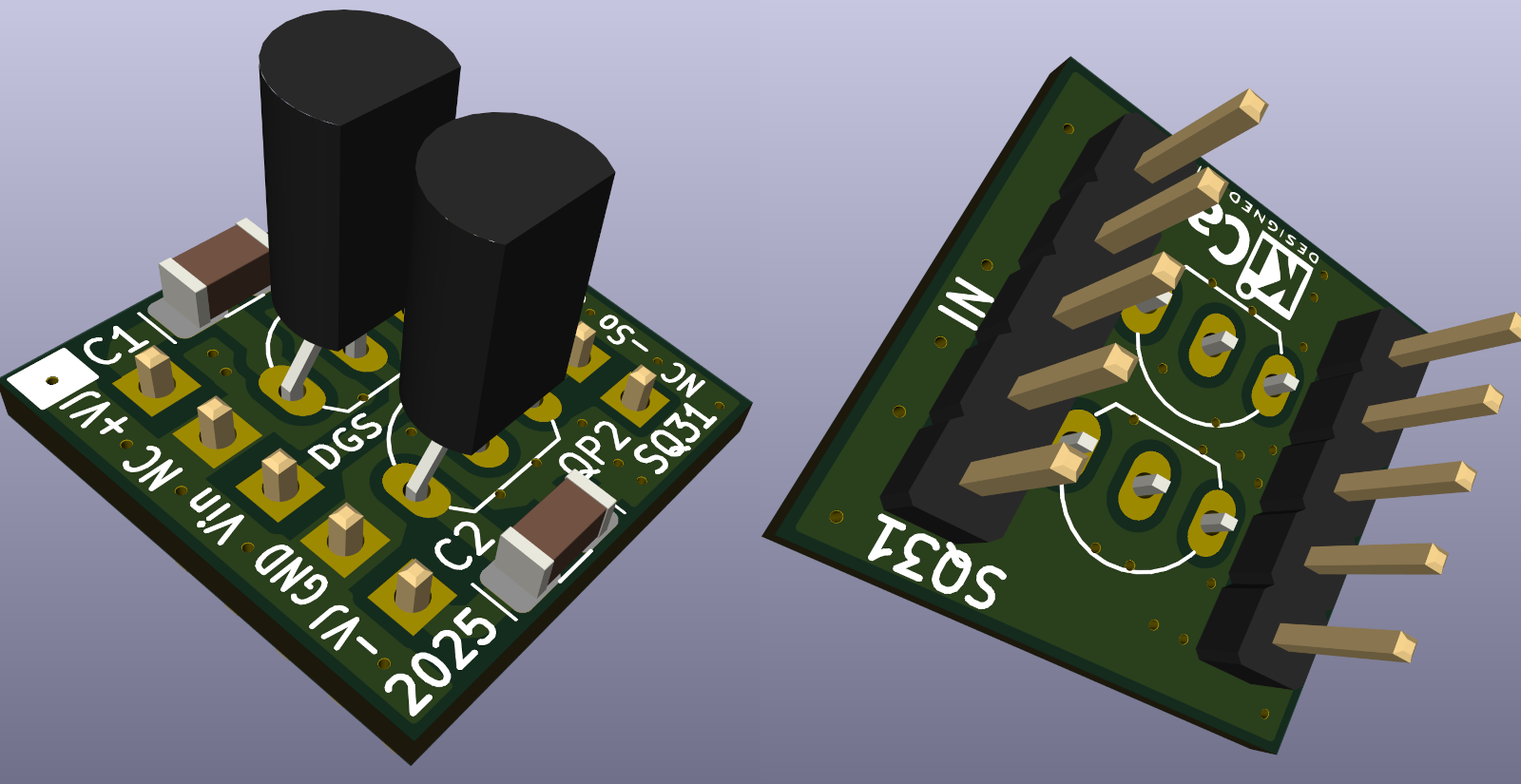

写真

HBC 全体の写真です。表面実装トランジスタを載せ細ピンヘッダーを付けています。

設計

JFETでは大抵は大丈夫だと思いますが、Pchのソース・ドレインを逆に使っています。

パターン単純化するためだったとはいえ、(逆の利用については)半導体メーカーは特性保証していないので非推奨となります。プリント基板は2層(表・裏)です。

なお VccJ± と VccB± は実際には同じ電源を供給しますが、モジュール内では分離してデザインします。

JFET選別作業について

国産JFET もわずかに現行品もありますが、製造終了品の在庫なども探せばあるかもしれませんが、

ランクが揃ったPch・Nchは購入できないと思われます。

海外JFET も コンプリメンタリペア として売っているわけでは無いので、

同一メーカーのNch・Pch JFETをかなり大目に購入して、

Idss選別して組み合わせる必要があります。

日本製JFET だと例えば Idss は GR/BL/V とかランク分けされているものもありますが、海外製だと型番が違って用意されていることがあります。

何種類か購入しましたが、Idssは2mA~30mA位でバラついててペア組み合わせるのが相当難しい状況でした。

なお多少の Pch・Nch 特性差異については調整・吸収できるプリアンプ回路構成となっており実用上は一応問題ありません。

BJTについては国産メーカーも現行品のコンプリメンタリ品が数種類あります。 低雑音品あるいは音の好みなどで選ぶことができます。

計測・テスト

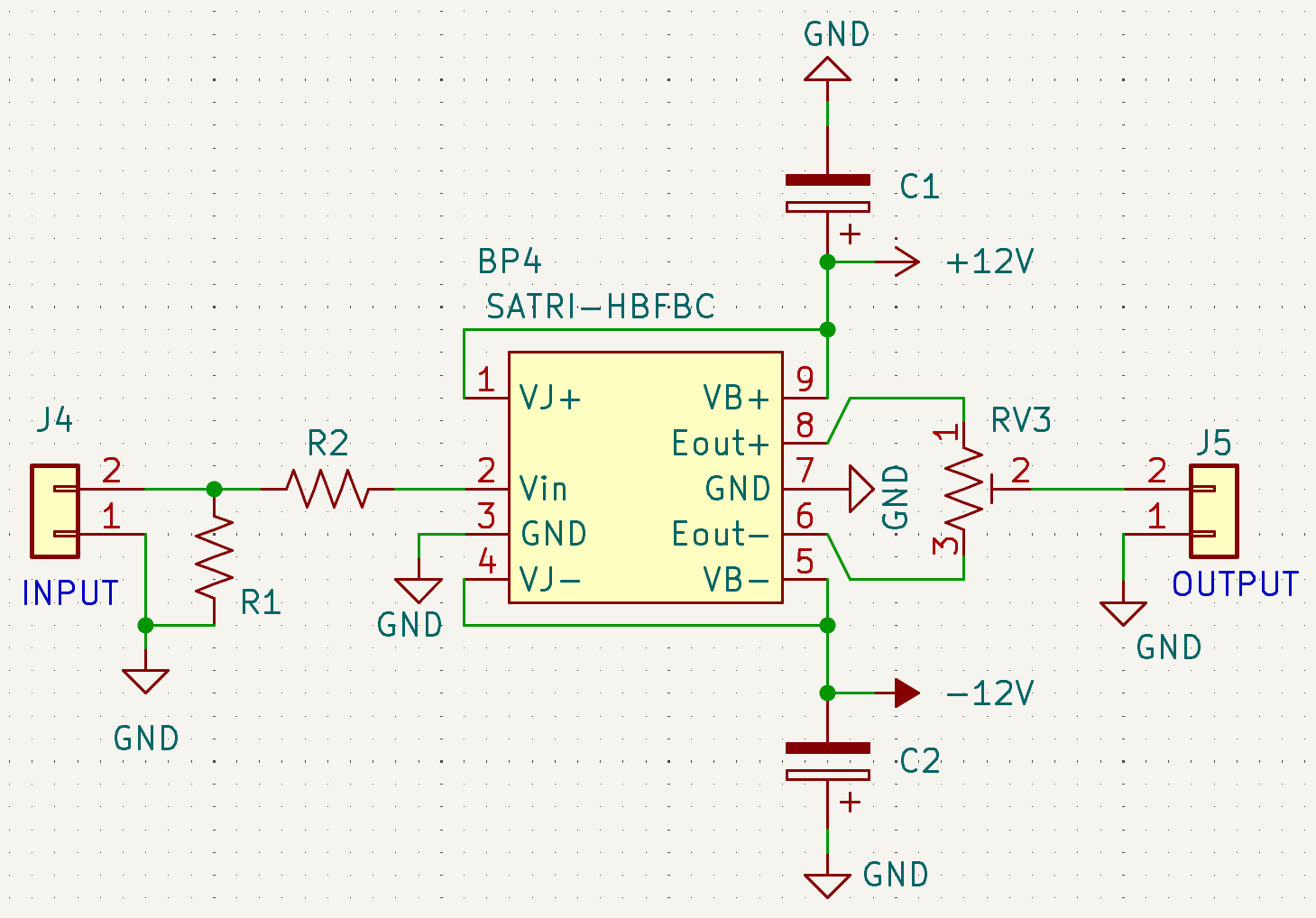

バッファ基板ということで正負電源と抵抗繋げばゲイン1倍のアンプとして一応使えます。

最小構成の使い方としては以下。

ブレッドボード上に構成してサイン波を入力して出力信号をオシロスコープで計測します。

なお写真では数種類作ったバッファモジュールの出音傾向が知りたくてイヤホンを駆動させています。

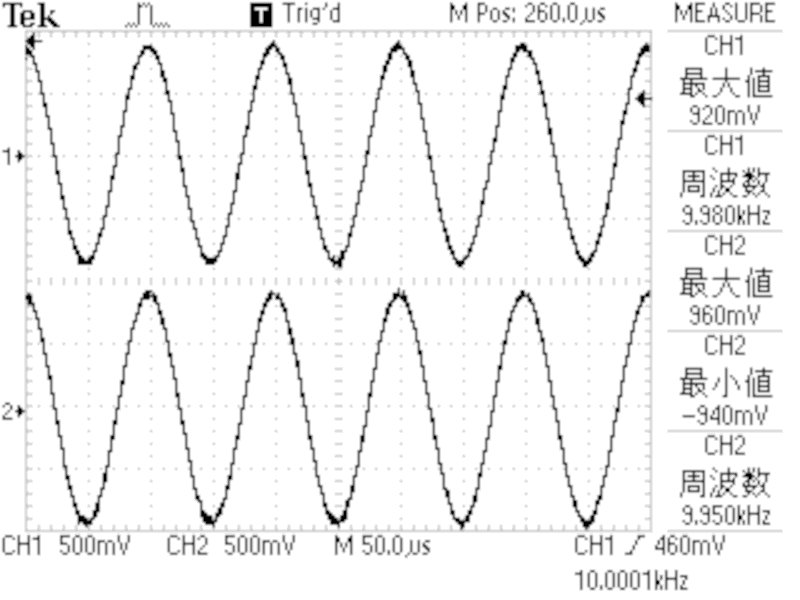

詳細確認としては、サイン波を入力してオシロスコープで計測します。

正常波形であるか、発振していないかなどを順次確認します。

設計補足、部品留意点、製造留意点

- バッファHBCはJFETのIdss値に影響を受けます。テスト回路の可変抵抗RV3には注意が必要でして、 Idss値が数mAと小さければ 多回転100Ω でよく、Idss値が10~20mAと大きければ 多回転500Ω を推奨します。 これはPch/Nchの差異を取り切れないことがあるためです(※出力にオフセット電圧が出てしまう)。

- BJTアイドリング電流もエミッタ抵抗RV3の影響を受けます。トランジスタが触れないほど熱くなる場合は抵抗を大きくして電流を下げる必要があります。

- 調整箇所が無いので、逆にトランジスタ選定を考慮する必要があります(JFETやBJTのランク等)。

- 発振したときの対処法も未考慮でして、出来るのはモジュールの外にあるJFETゲート入力抵抗が100Ωであれば1kΩなどに増やす案、 (動作確認の回路例の)C1・C2に低ESR固体電解コンデンサを利用してかつモジュール近傍に配置する案くらいだと思います。 (※対策用に、電源ピン近くにMLCCパスコンを増設できる予備パタンを用意しておくべきでした)

- オフセット調整方法についてはプリアンプ基板の記載を参照。

感想・反省点・今後の課題

Pch・Nch JFET の特性近づけることも相当困難で、プリアンプ基板に用意してあるオフセット調整の可変抵抗も大きく補正する必要がありました。 (プリアンプ基板でのボリューム変更時にDCサーボが切れたときに)出力のオフセット電圧も出易くもなります。 音の精度含めてまだまだ改善課題が複数あると認識しました。

音は使用するJFET品種やメーカー、Idss値で結構印象が変わりました。 トランジスタを変えて数種作ってみて比較試聴して、元気で音が前に出てくる組合せのものを採用しました。

コンポーネント:HBD v1 (高精度 JFET-BJT バッファ基板 v2)

概要

『 HBD 』は前製作 HBC から大幅改善を行ったバッファ基板です。

作業時期は、設計着手 2023年10月 、音出し 2023年12月 です。

JFET入力・BJT出力 ということで「異種=ハイブリッド」なバッファ回路となっています。

プリアンプ基板にて必要となる部品で、HBC(HBFBC) ピン配置になっています。

最初に作成した HBC では、手に入る現行品の表面実装 JFET はかなり限られており、 選別してもPch・Nchの特性を近づけることが難しくもあり、 (プリアンプ基板の)オフセット調整用可変抵抗で無理やり差異を抑え込んでいました。音質面・精度面でも改善したい点でした。

ここで TI社 の BurrBrown ブランドで超低雑音・超高性能ローノイズJFET JFE2140(デュアル)、

JFE150(シングル)がありました。ものすごい性能です。

是非使ってみたいと考えていたものの Pch JFET は発売されなさそうでした。

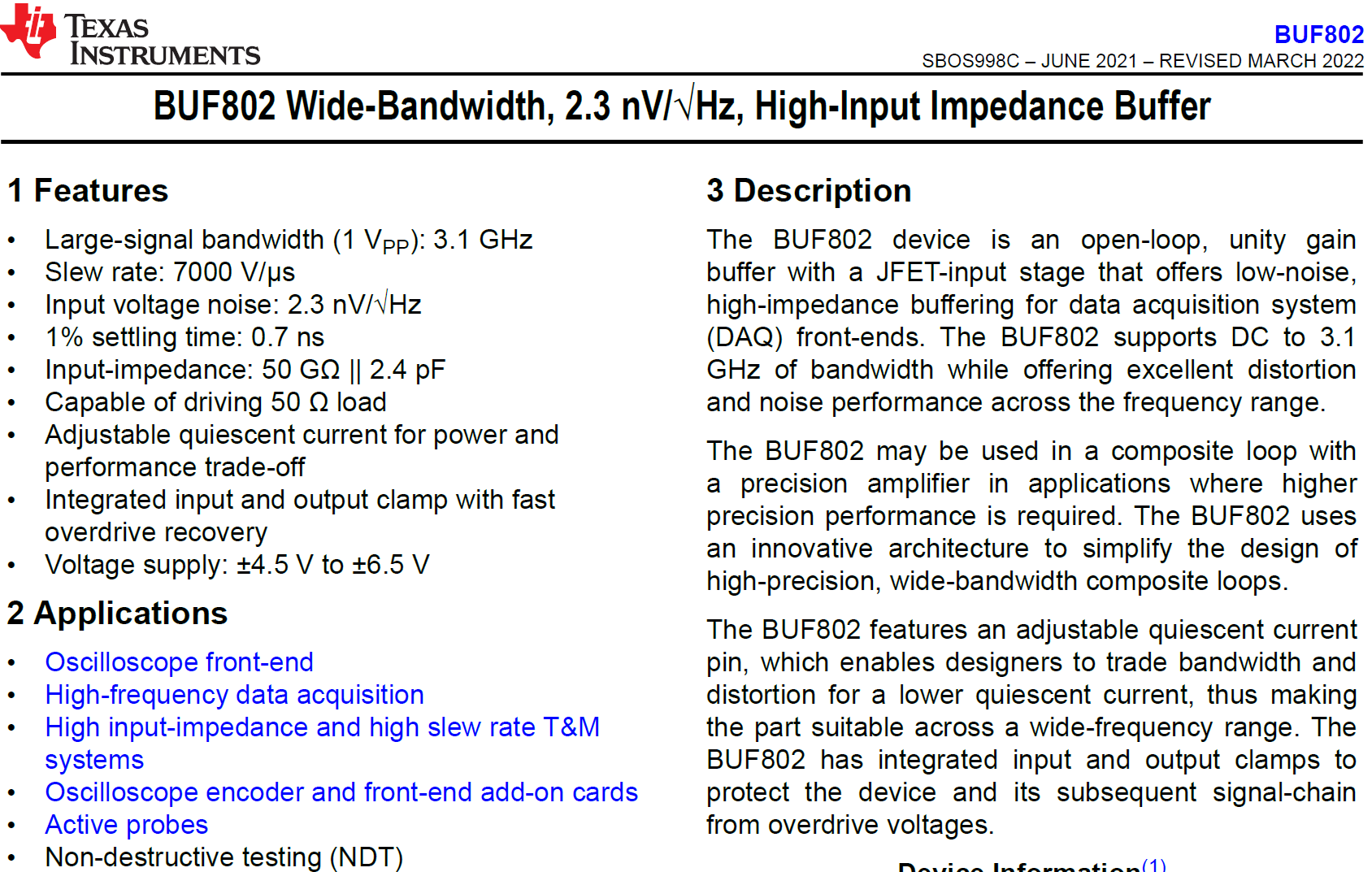

更に技術情報を色々調べていると TI社 の 計測機用バッファ BUF802 というものがあることが分かりました。

耐圧不足で当プロジェクト用に直接利用することはできませんでしたが、

データシートの等価回路を参考にして新たな入力バッファを検討することとしました。

これらとこれまでのノウハウを組み合わせると、JFET入力・BJT出力の高精度バッファ回路 を編み出すことが出来ました。 思い描いていた 高精度ハイブリッドバッファ を実現することが出来そうです。

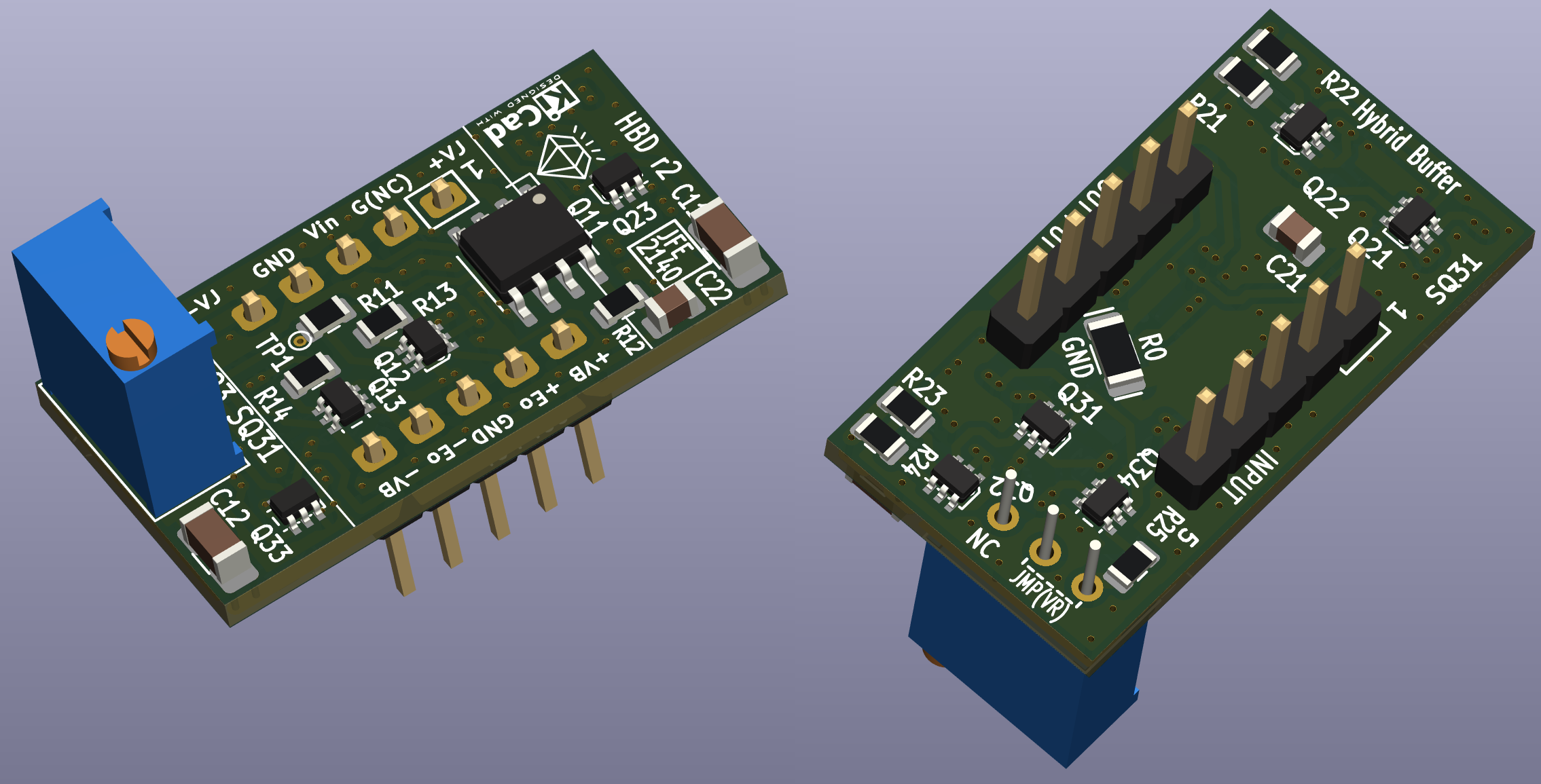

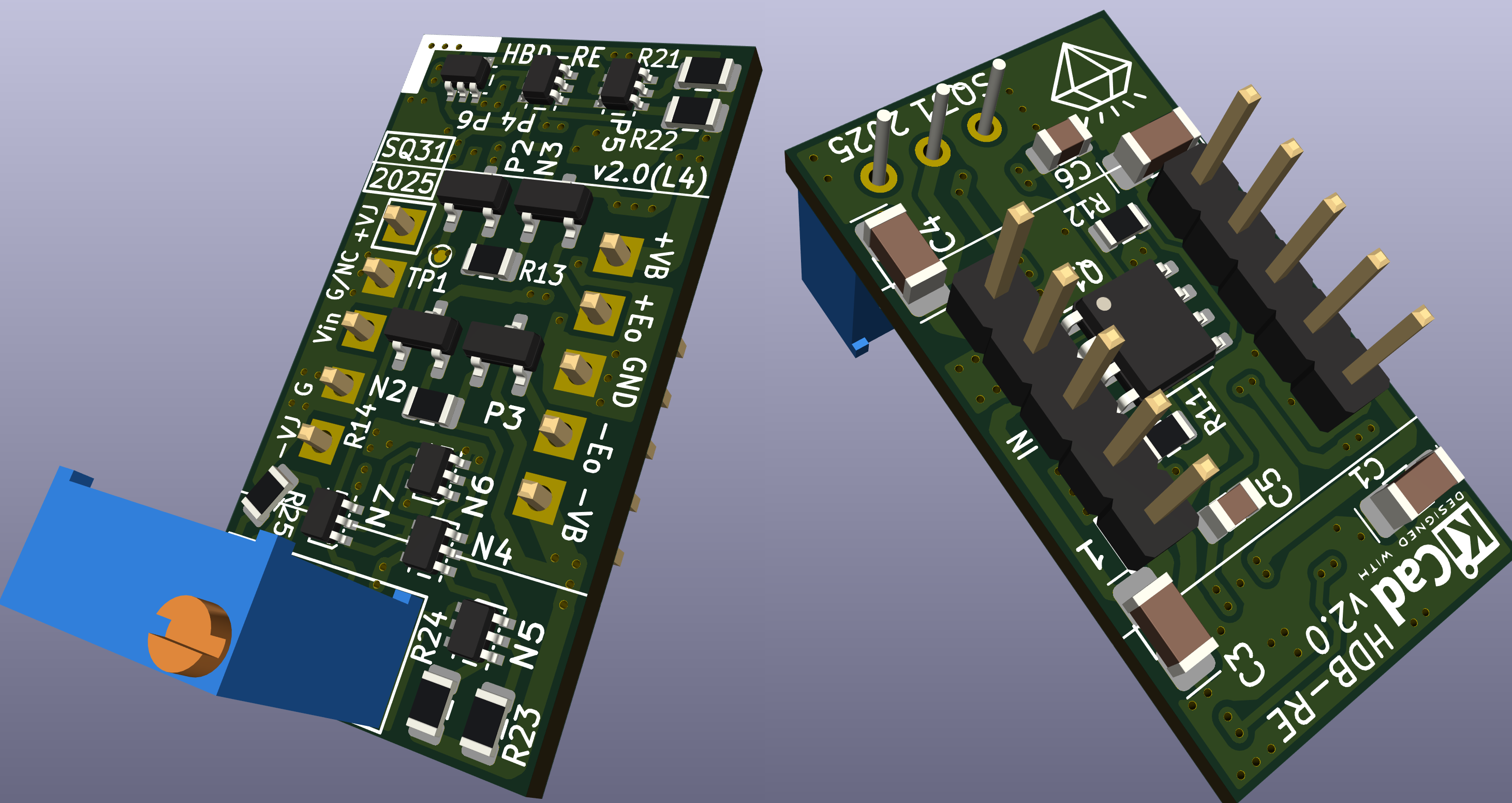

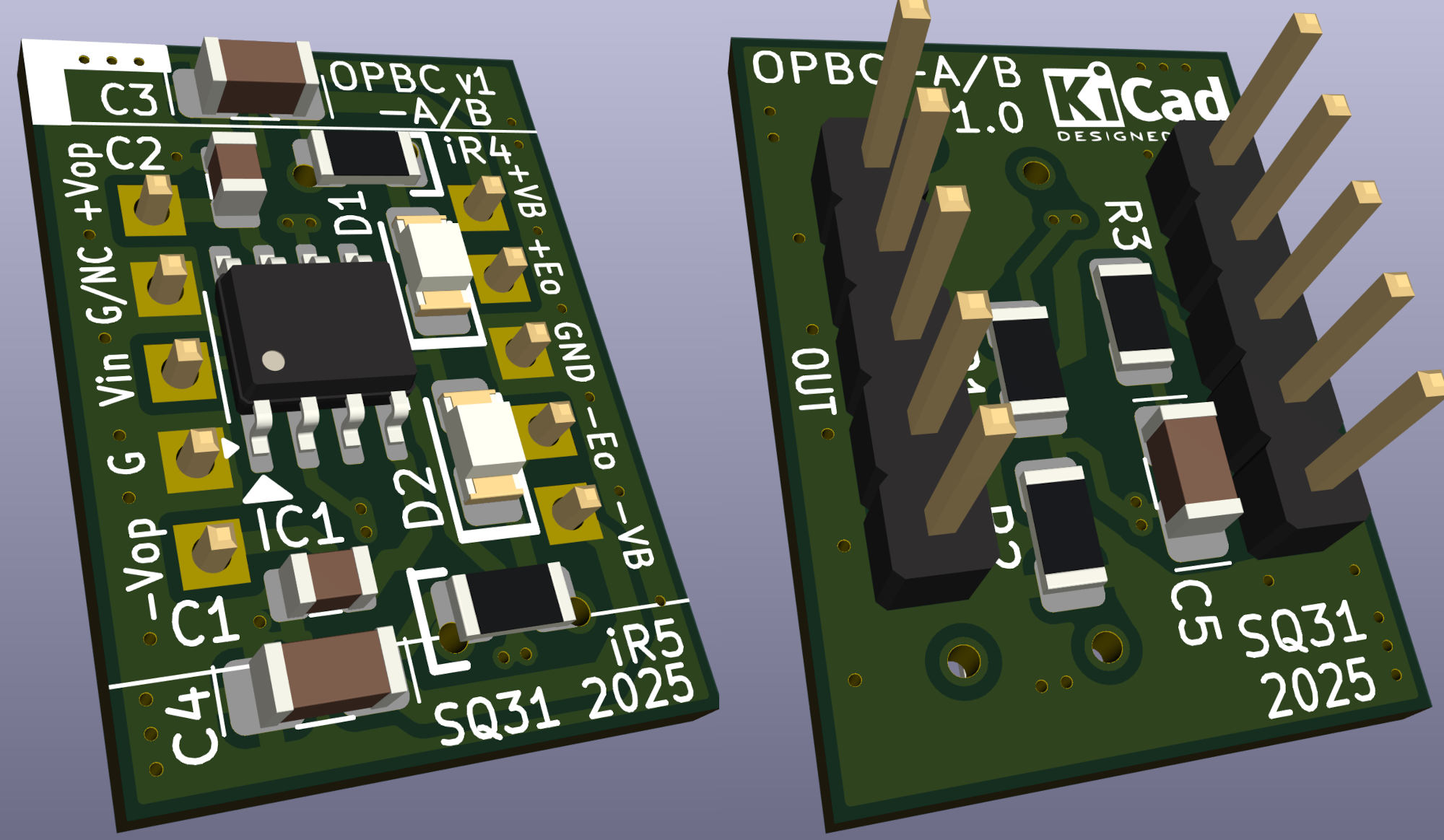

写真

HBD 全体の写真です。

HBDでは 小型デュアルトランジスタ SOT363-6 サイズが表面裏面の合計で9個も乗っていて製造するのも超大変でした。

新旧バッファの比較です。

左:HBC、右:HBDはピンは全く同じ配置ですが、HBDでは部品を載せるために基板サイズは結構縦長になってしまいました。

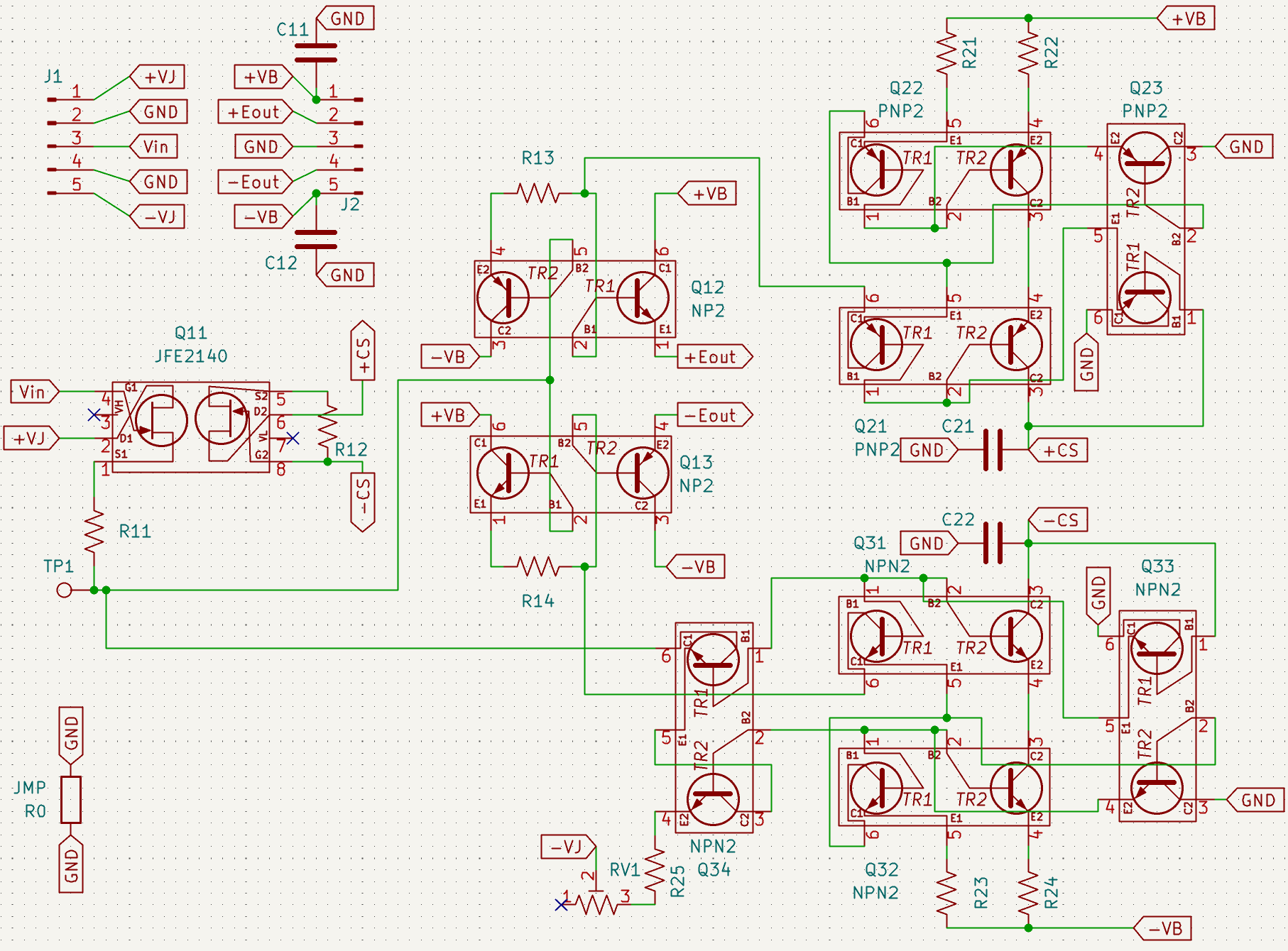

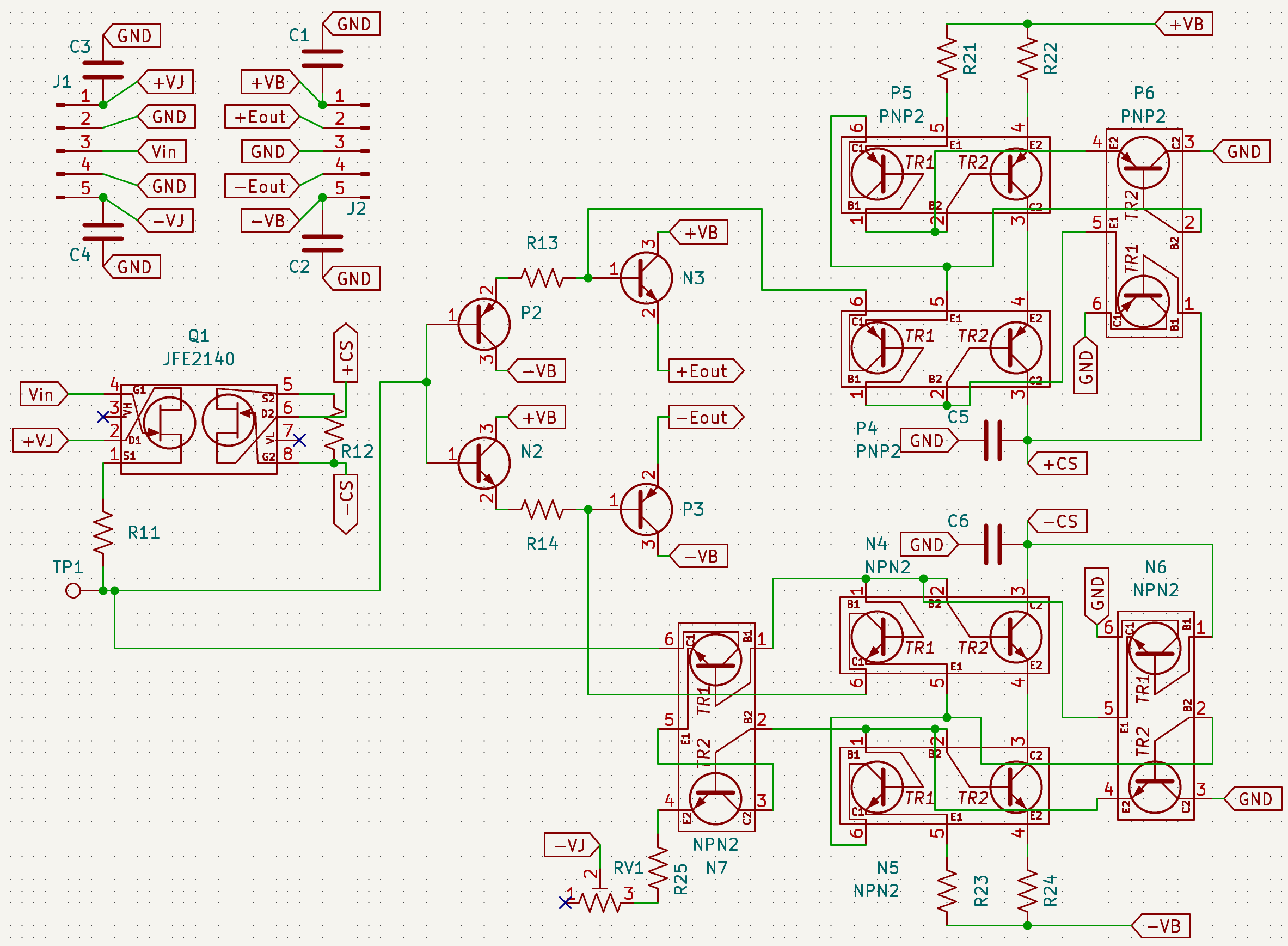

回路図

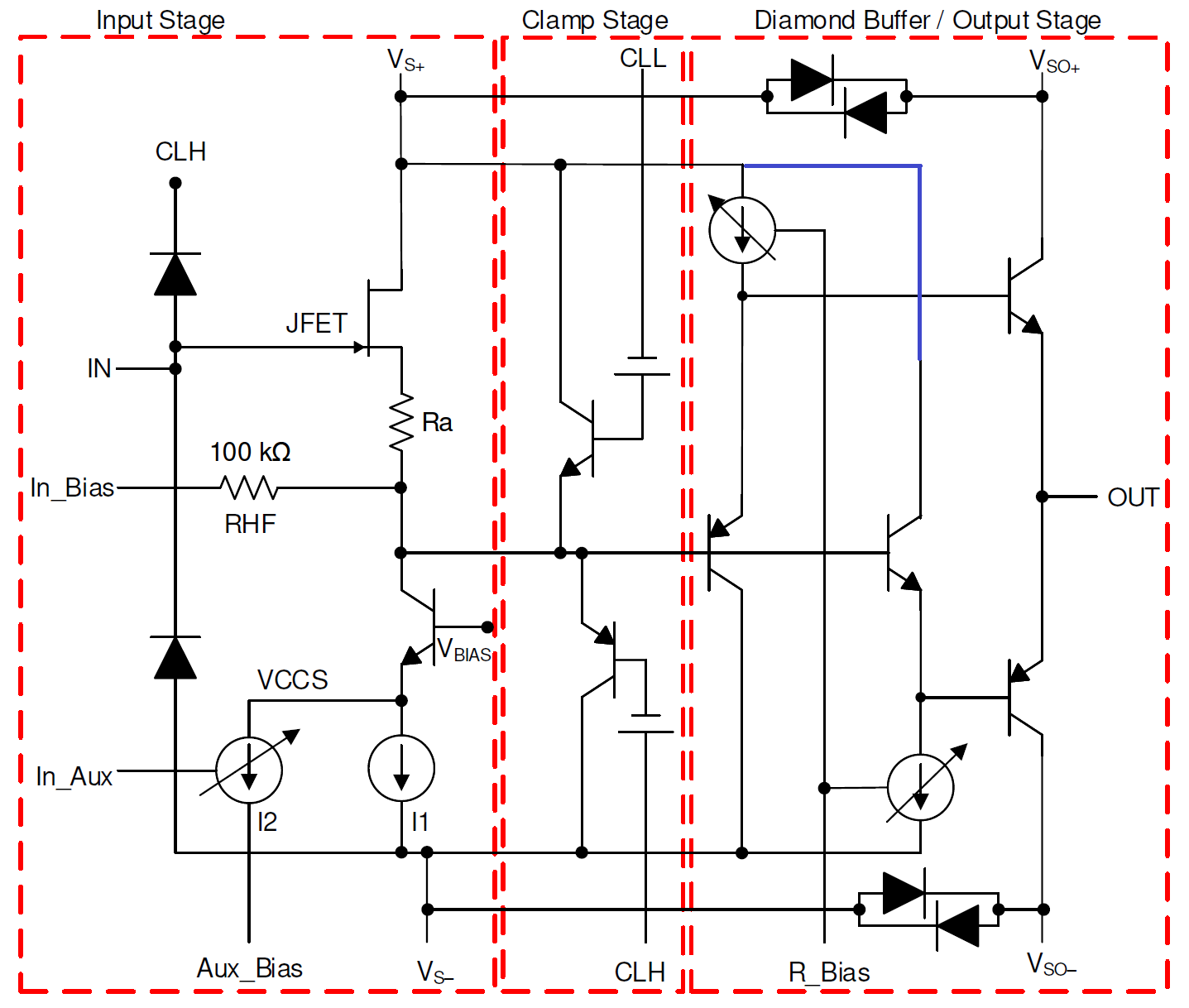

電流源を構成する カレントミラーもLTspiceシミュレーション で色々比較検討して詰めています。

カレントミラー最小構成 はトランジスタ2個ですが、トランジスタ4個あれば「1: 高精度ウイルソン型 」を構成できます。

その他にも色々検討できます。

上記回路図のカレントミラーは複雑な構成になっています。回路的には「2: 高精度ウイルソン + ベース電流補償型 」となっていて、 下側は更に1入力2出力タイプです。

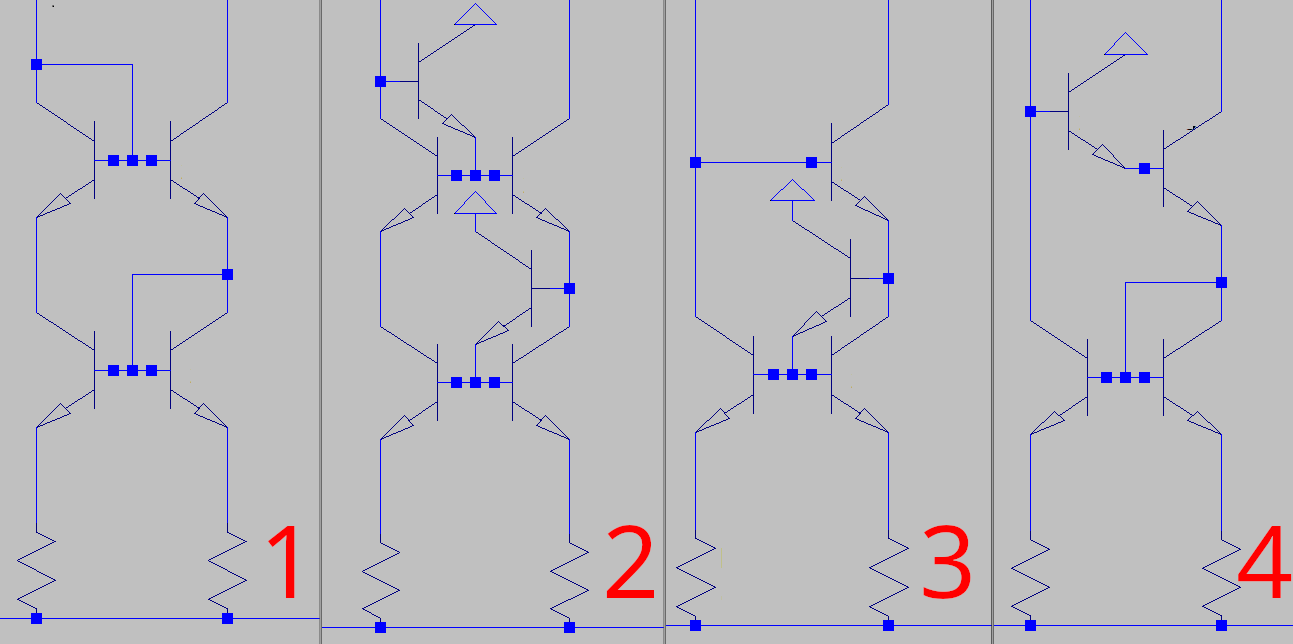

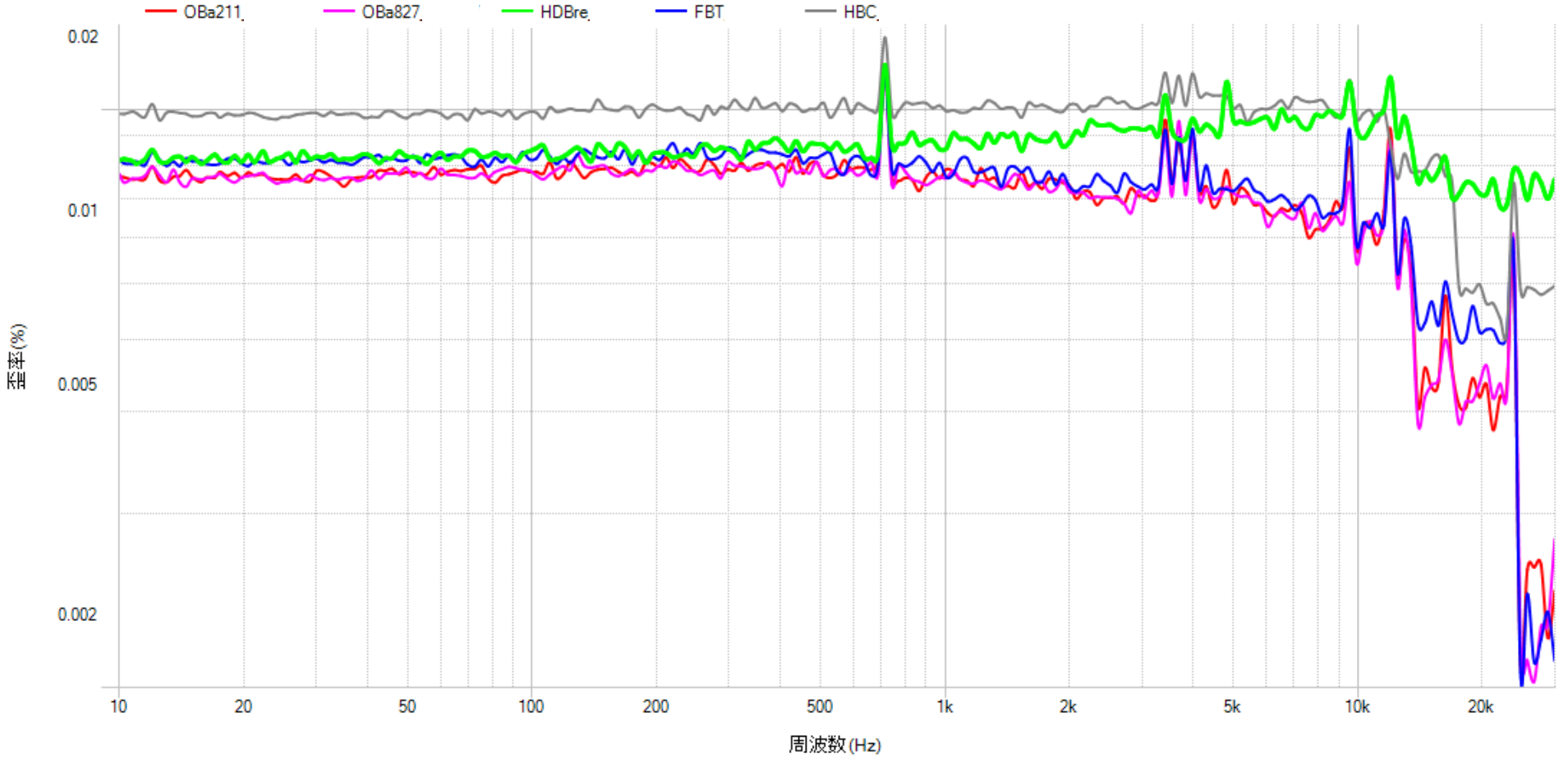

カレントミラー回路のアイデア別に、横軸に入力信号周波数、縦軸に LTspiceシミュレーション結果 の 歪み率 をグラフプロットして比較検討しました。

それぞれの詳細は割愛しますが、「2段v9L」が今回採用した回路案のグラフでして高い周波数まで精度維持しています。

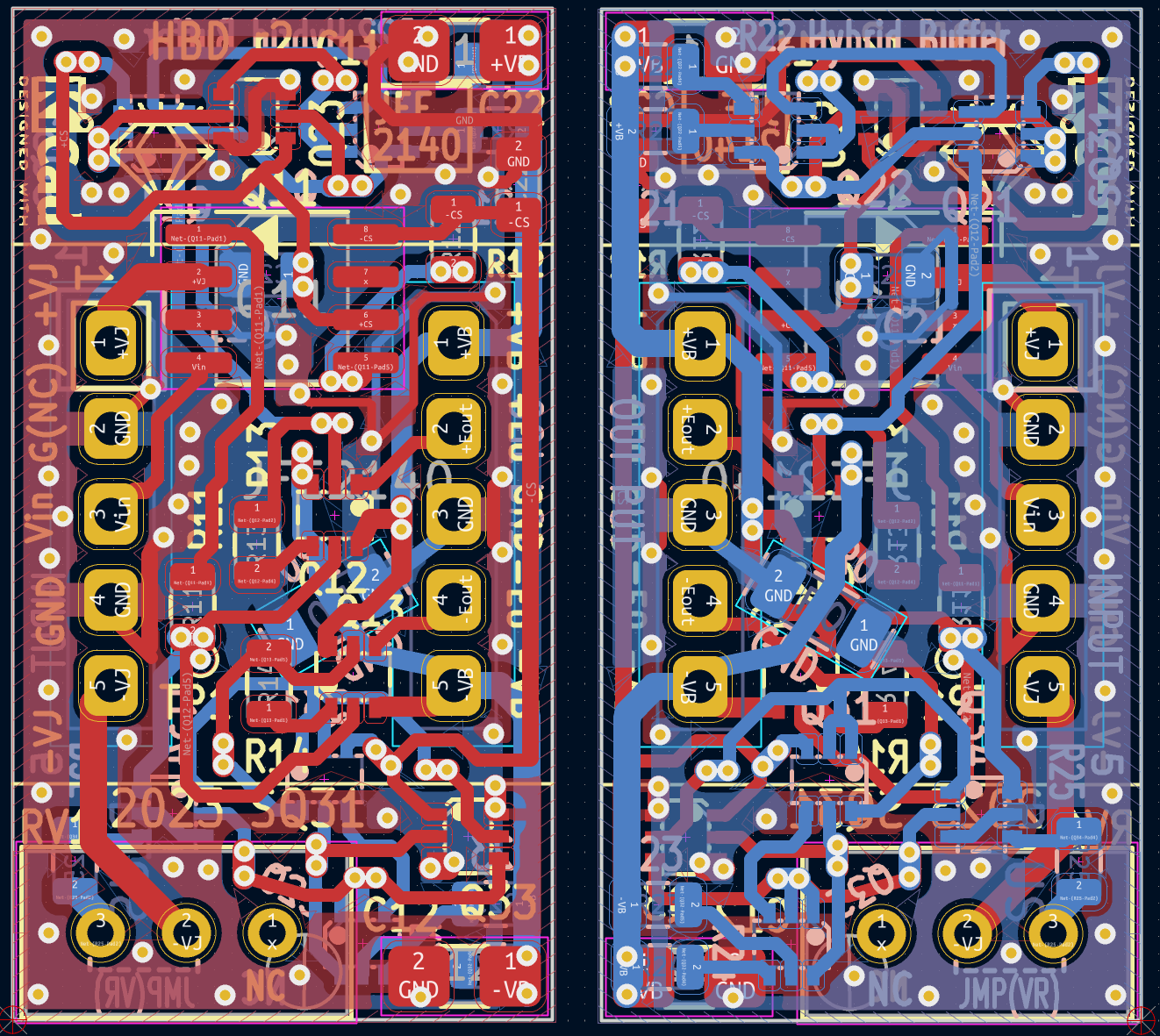

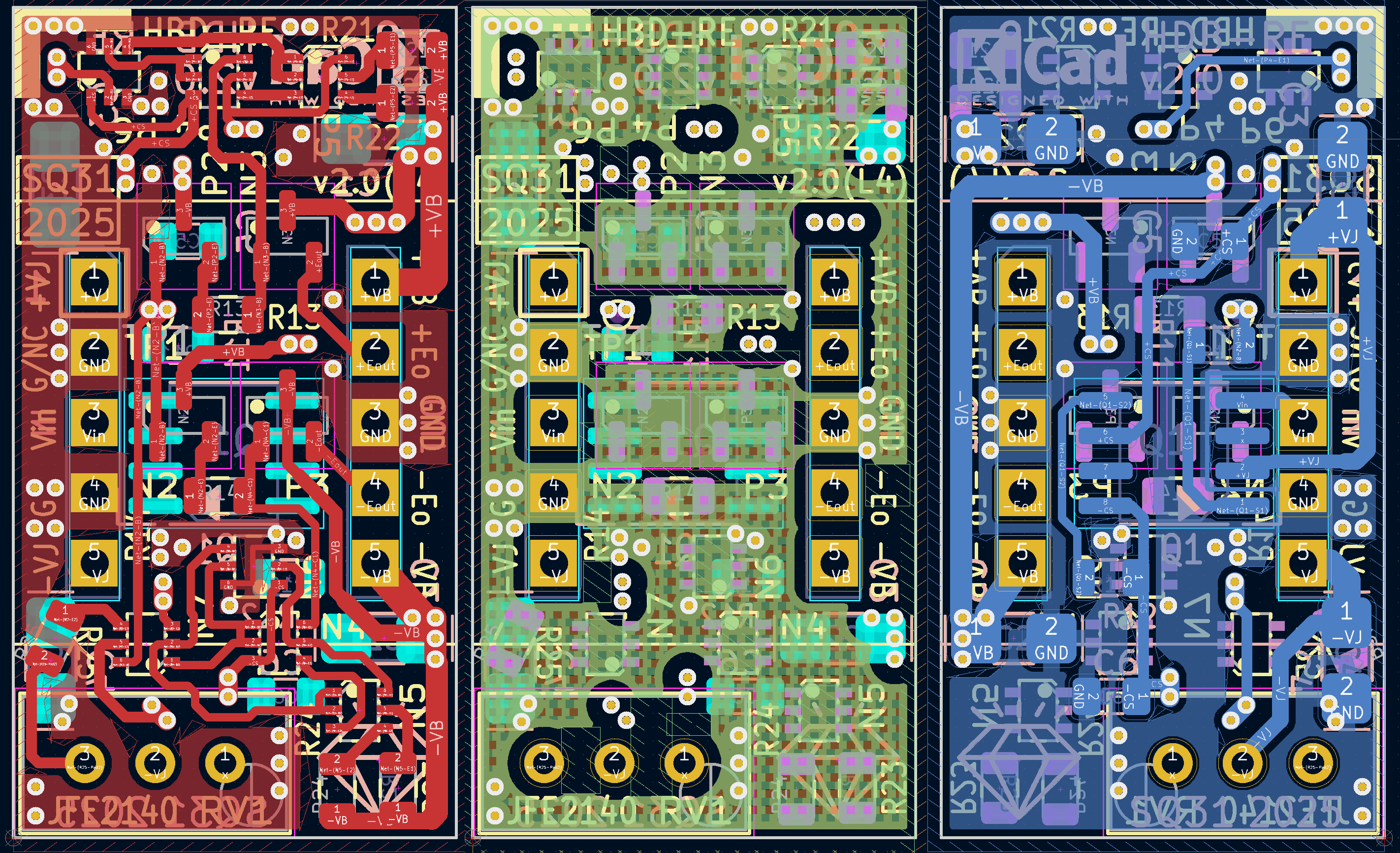

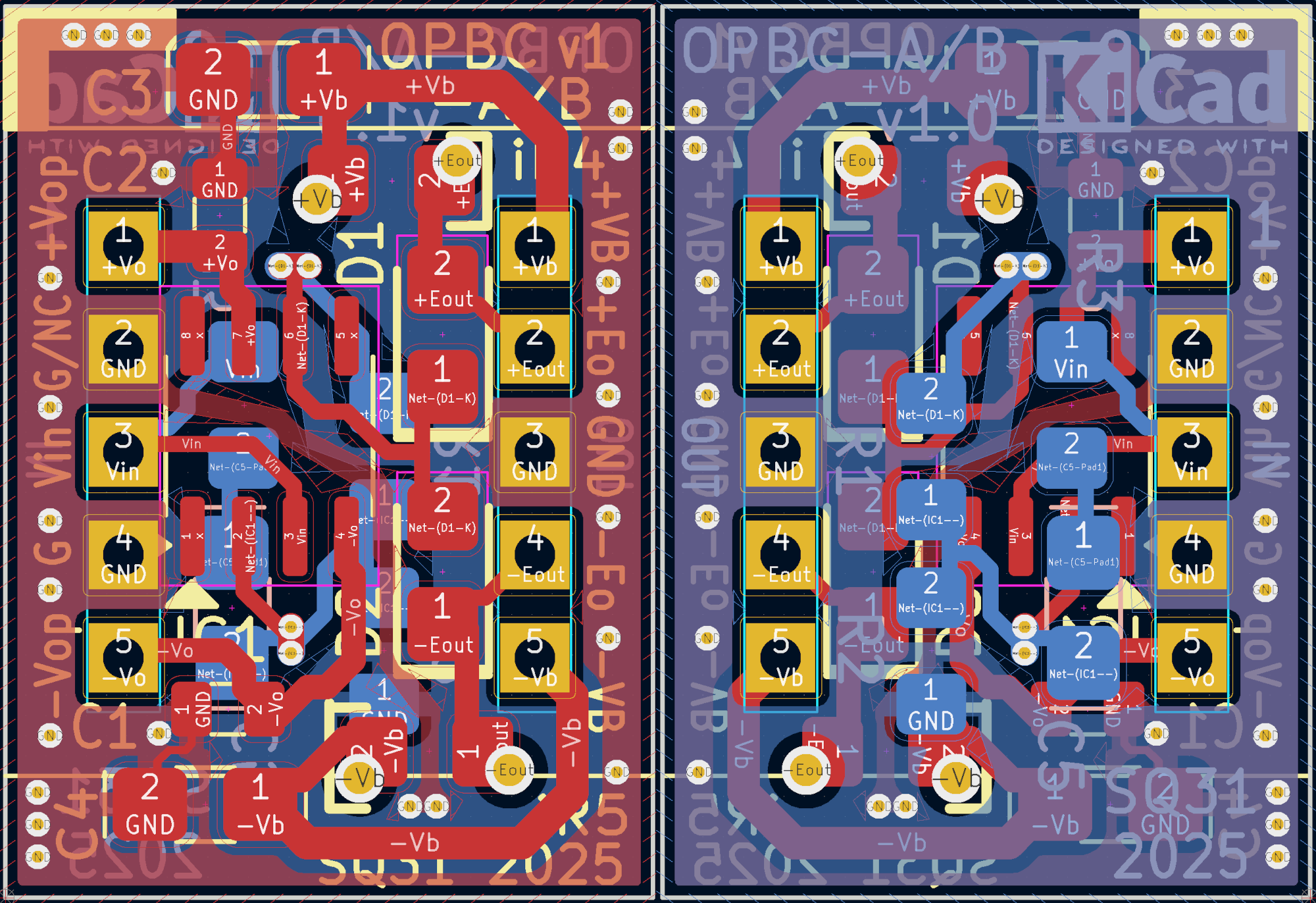

基板デザイン

本回路のプリント基板デザインでは、手作業で一から引くととても配線しきれず早々に断念しました。

代替案として、部品を適当に配置をかえつつ自動配線をおこないそれを複数回試行する方法としました。

色々自動で作らせてみて良いものを位置微調整して再度自動配線ということで煮詰めていき、最後には手作業で改めて配線清書しました。

プリント基板は2層(表・裏)です。

フットプリントはもともとピン9本ですが、未使用を追加GNDとして用意しました。逆差し防止で1本削ってもいいし、

使用してGND強化してもいいし、どちらでも出来るようにしました。

あと JFE2140 のデータシート にはプリント基板のパターン留意事項が記載されています。音質追求のため可能な範囲で指示を取り込むようにしました。

調整用の可変抵抗に大きいものを使っていますが、精緻な電流調整が必要なので多回転の縦型が不可欠でした。

あと3Dでは余裕があるように思えたのですが、実際に製作するときは素子間の隙間が狭くて苦労しました。反省点は多かったです。

調整方法

前製作 HBCと同様に動確用ブレッドボードを用意するか、あるいはテスト基板を用意したうえで調整を行います。

- 初めにJFETの調整を行いますが、基板上の可変抵抗を使います。 入力とGNDをショートして入力0Vの状態のときに、テストポイント(TP1)が0mVに近づくようにします。 JFE2140が少し温まってから調整した方が良いです。

- ただしBJTエミッタフォロワのオフセット調整については本モジュールのみでは調整できません。 別途、プリアンプ基板側のエミッタ可変抵抗を調整します。オフセット調整方法についてはプリアンプ基板の記載を参照。

- ダイアモンドバッファの調整は表面実装抵抗(R13、R14)の付替えが必要です。最初作るときは、あらかじめ複数定数を用意した方がよさそうです。

計測・テスト

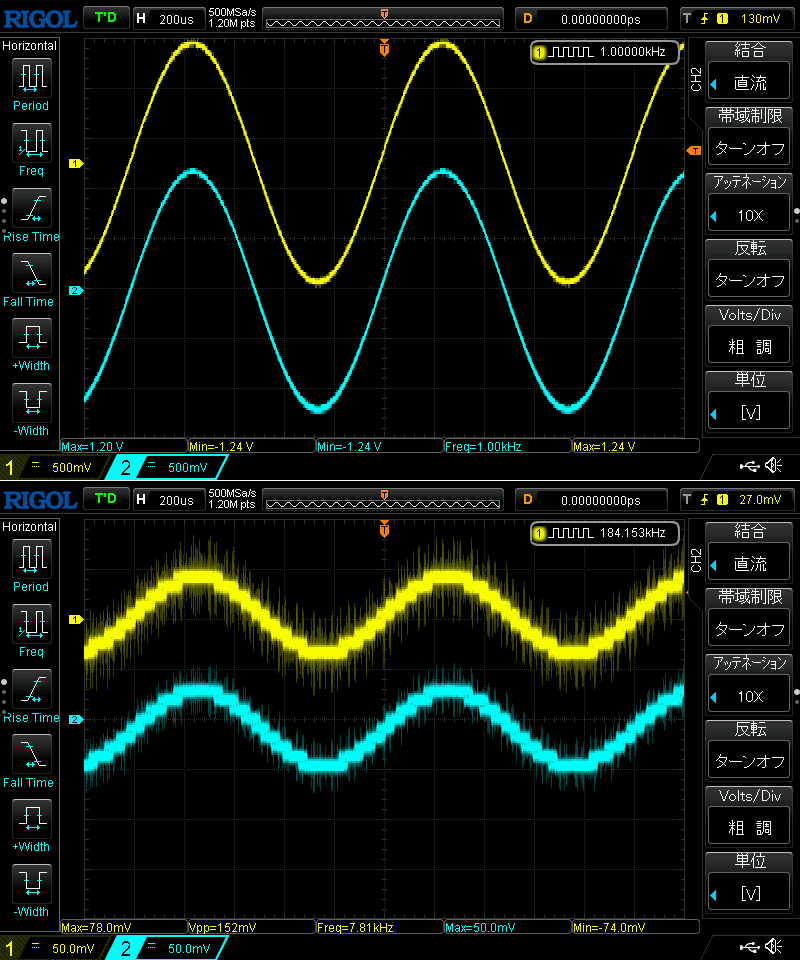

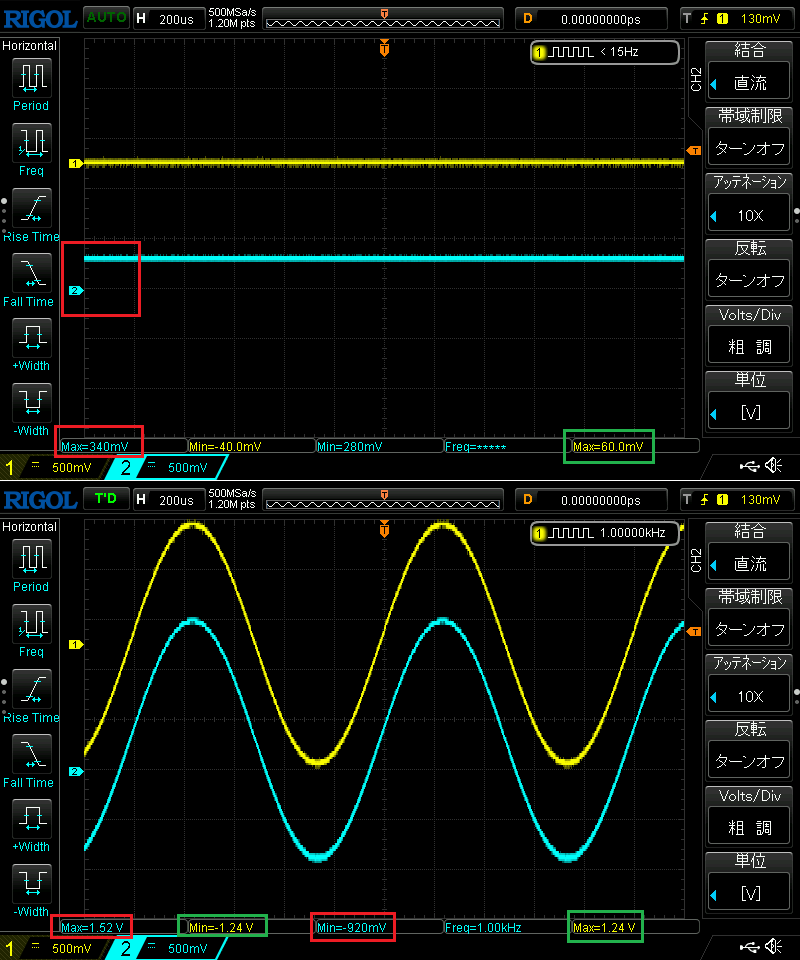

オシロスコープにて順次計測を行っていきます。

1KHzのサイン波が正常に出力だったとしても、小信号だと高い周波数での発振観測されたりすることもあるので

波形:左のように色々信号を入れて確認します。

なお波形:左下は高い成分が乗っているようにも感じますが、

近くのLED電灯ノイズだったり、ACアダプタ(スイッチング電源)のノイズだったり、

プローブ引き回し由来だったり、素人計測では色々拾ってしまうようです。難しいですね。

波形:右はハンダ付け不良により水色側に異常なオフセット電圧が乗っています。

(入力をGNDに繋いで入力0Vとして)入力信号切ると分かります。ハンダ付けミスを探して修正しました。

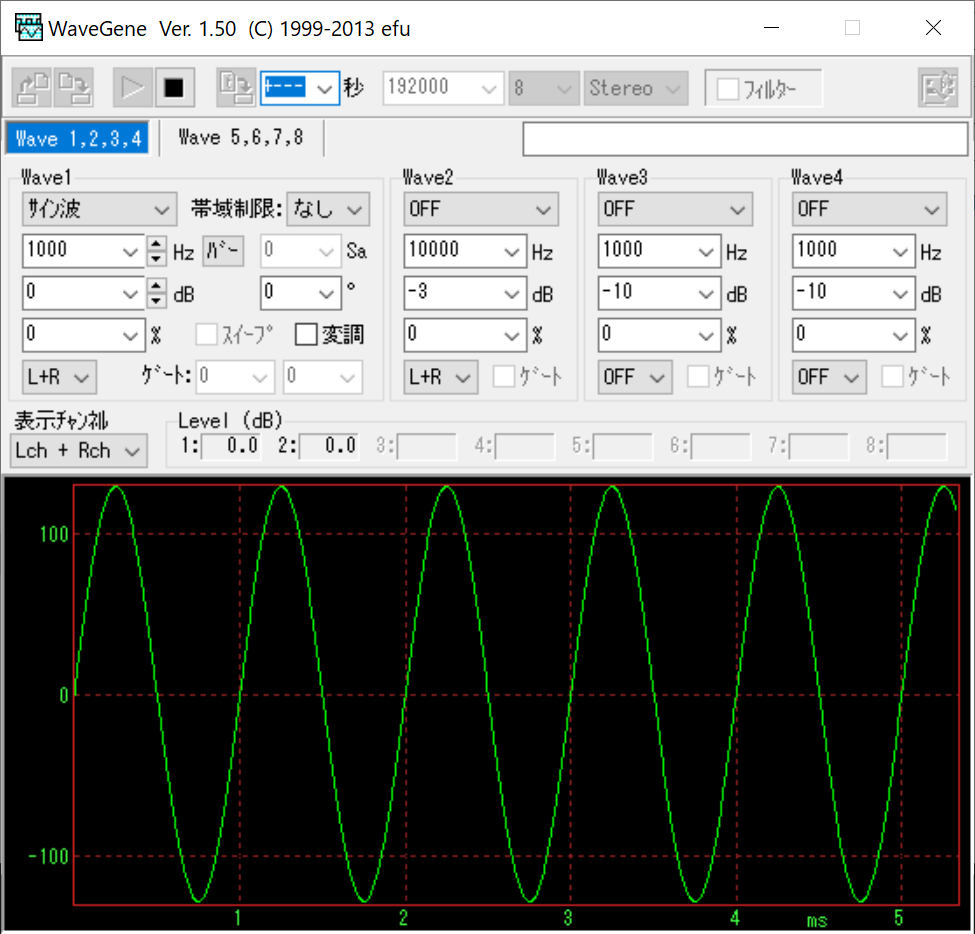

テスト入力信号のサイン波の発生にはPC用の信号発生ソフトを使っています。efuさん作の WaveGene というソフトです。

2024年9月からweb archiveではなく本家からダウンロード可能となっています。

https://efu.sub.jp/soft/wg/wg.html

PCサウンド機能を使うことになるのですが、

きっちりテスト信号出すなら廉価品でいいのでDTM入門機とかのオーディオインターフェイスが良さそうです。

設計補足、部品留意点、製造留意点

- dual BJTについてはマッチドペア品種を想定してます。Tr1とTr2との特性が近いため高精度なカレントミラーを構成することができます。

- JFE2140の動作時の電流値はデータシート記載のローノイズ推奨値 5mA としました。

- 抵抗については表面実装チップ抵抗となりますが、コストパフォーマンスと音質から薄膜チップ抵抗を推奨しておきます。 逆に厚膜チップ(メタルグレーズ厚膜抵抗)は音質面から個人的には非推奨です。 ネット自作記事を探すと音質比較評価などもありますので、まずは音質評判が良くてコスパもよい品で試してみることを推奨します。

- 発振したときの対処法としては、予備C21・C22にコンデンサを実装する案、 モジュールの外にある(JFE2140)ゲート入力抵抗が100Ωであれば1kΩなどに増やす案、 予備パスコンC11・C12にMLCC等のコンデンサを追加する案があります。

- 電源パスコン C11、C12 はプリント基板パターンに余裕があったのでオマケで付けていたものです。 省略して問題ない認識でしたが実際に使ってみると音質影響が大きくて驚きます。 最初、村田製作所 MLCC 0.1uF ( C0G )を使ってみたのですが図太いアタック強い音になってしまい正直好みが分かれる音で驚きます。 パナソニック の ECHUフィルムコン を試しましたがこれは繊細さを維持して輪郭を少し強調するような味付けでなかなか気に入りました。 他の候補は ルビコン PMLCAP などがありそうです。 この音質変化については、ICモジュール基板も電源ライン直近パスコン実装を検討したほうが良い可能性があると示していると思います。 ただ部品品種選定や設置場所など考慮が必要そうです。

- はんだごて作業の後は フラックスクリーナー で基板を洗浄しておきます。コスパ・使い勝手から サンハヤト製 FL-500 を推奨します。

感想・反省点・今後の課題

HBDの音は、HBCと比べると格の違いを見せつけてくれます。 (使うJFET品種によりますが)HBCは元気な音ですが今にして思えば整理されていない音に感じます。 対して HBD では楽器の分離感もよく、それでいてボーカルの芯がしっかりしつつ音の透明感もアップして聴き入ります。 そもそも回路が違いますが音も全く違いました。

ただし、SOT363-6 (ピッチ0.65mm)について手作業ハンダ実装するのは結構大変であり、モジュールを複数個作っても全然慣れませんでした。 やはりリフローはんだ付けが望ましいのですが、本例HBDはトランジスタが表面裏面に配置されており、 自宅リフロー作業に適した基板構成となっていません。 自宅リフロー製造を目的に片面集約した HBD-RE (後述)を検討中です。

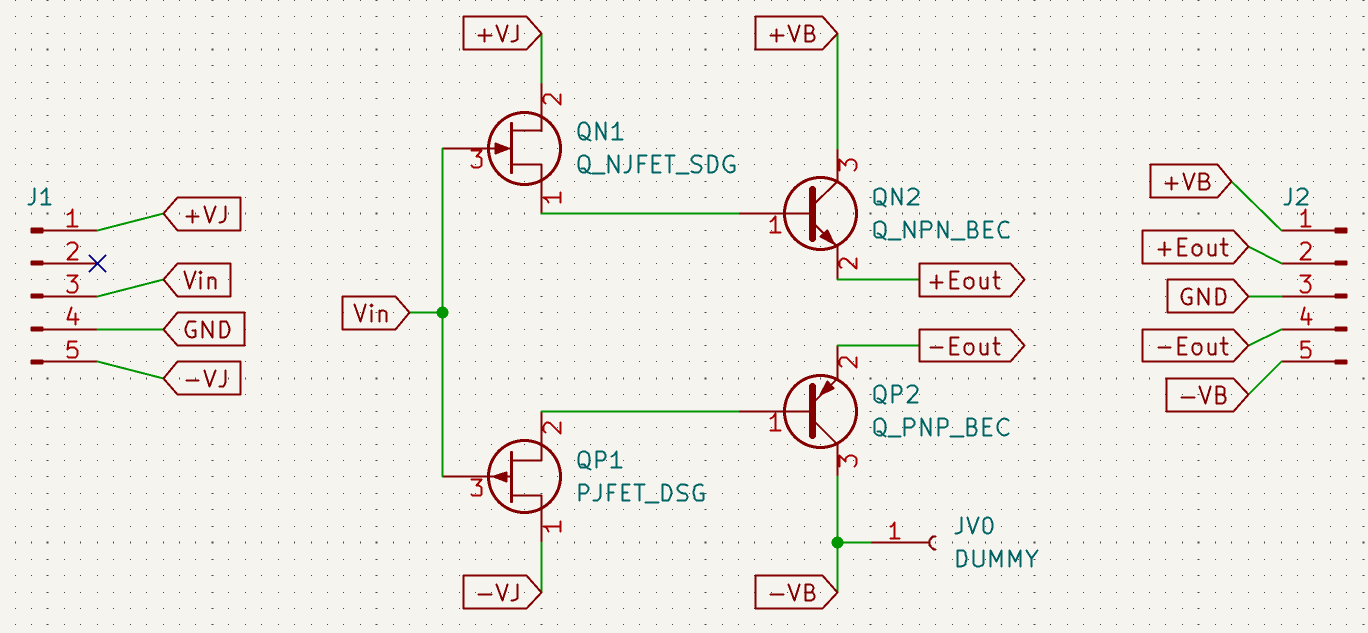

コンポーネント:HBD v2 (HBD-RE) (高精度 JFET-BJT バッファ基板 v3)

概要

HBD v1の表面実装 BJT を片面に集約して、自宅リフローはんだ製造しやすいように見直したものです。

写真は、青:HBDv2 (HBD-RE)、 緑:HBDv1 です。

設計

回路自体はHBDv1とHBDv2は同じといってもいいのですが、

ダイアモンドバッファのトランジスタをBJT DUAL (NPN-PNP x2)から、シングルBJT (NPNx2 + PNPx2)のローノイズ品に変更しています。

原理的には熱結合したデュアル品が優れているとは思いますが、聴感および許容損失などの面から上回ると判断して見直しました。

プリント基板は表裏2層で配線は済ませていますが、中間2層GNDを足して4層でデザインしています。

ノイズ対処面・熱対処面で効果がうまく出てるとイイのですが、素人の私では評価が難しく。

製造・計測

リフロー作業にてモジュール基板の大部分を製造できるようになりました。

更にデジタル顕微鏡を使ってチェックやリフローハンダ不備修正作業を行います。

以前と比較すると作業効率がとても上がりました。

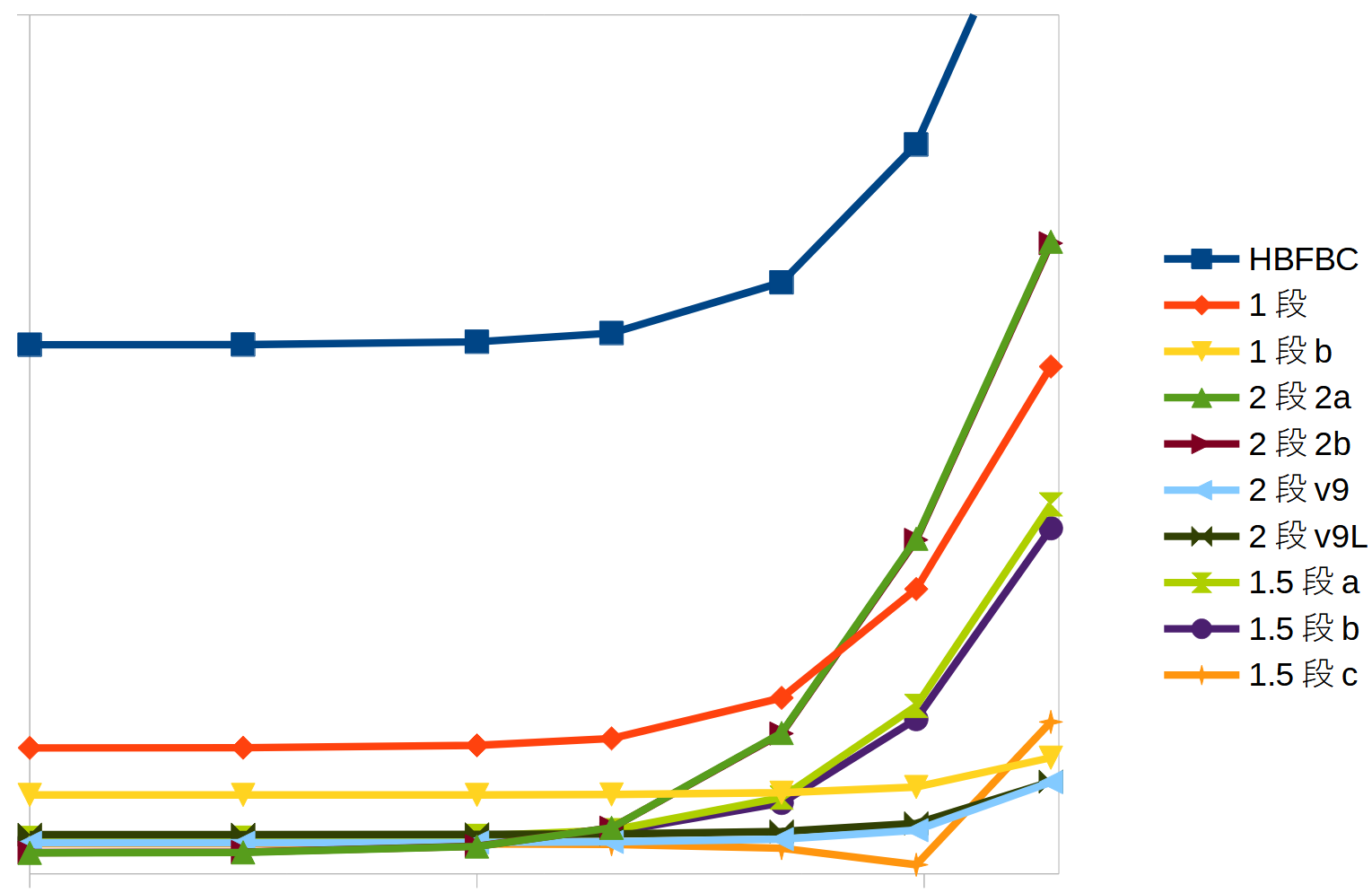

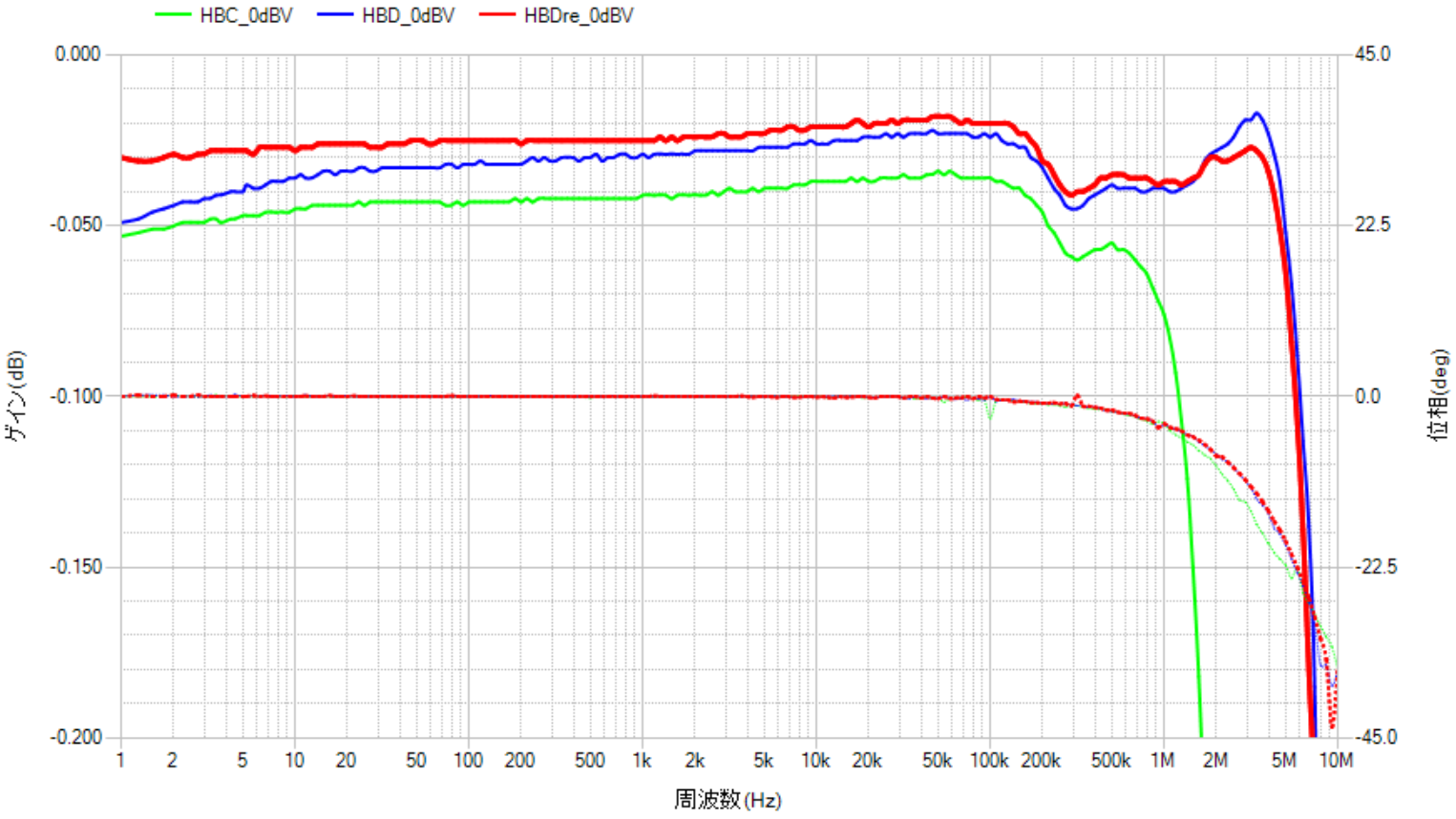

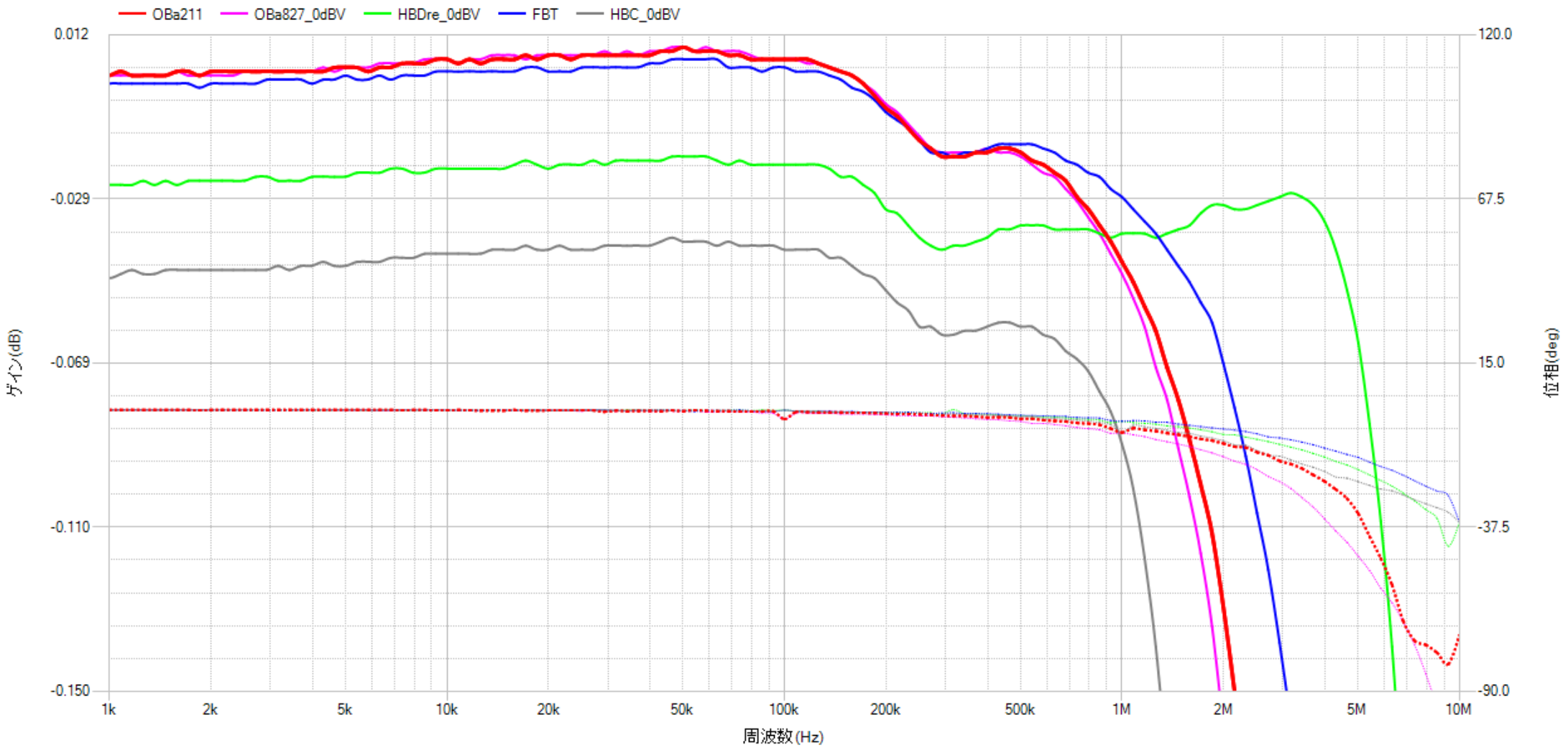

計測ツール(Analog Discovery2 + 自作テスト基板 + ソフトFRAplus)で評価してみると進歩しているようにも感じます。

旧HBD v1(グラフ青色)、新HBD v2(グラフ緑色)若干ですがよりフラットになってる感じもします。

感想

音の経路のトランジスタを変更してパタン改善したことなどもあり出音は少し変わったと感じます。 それよりなによりモジュール1個作るときの時間が結構短くなったのが嬉しかったですね。

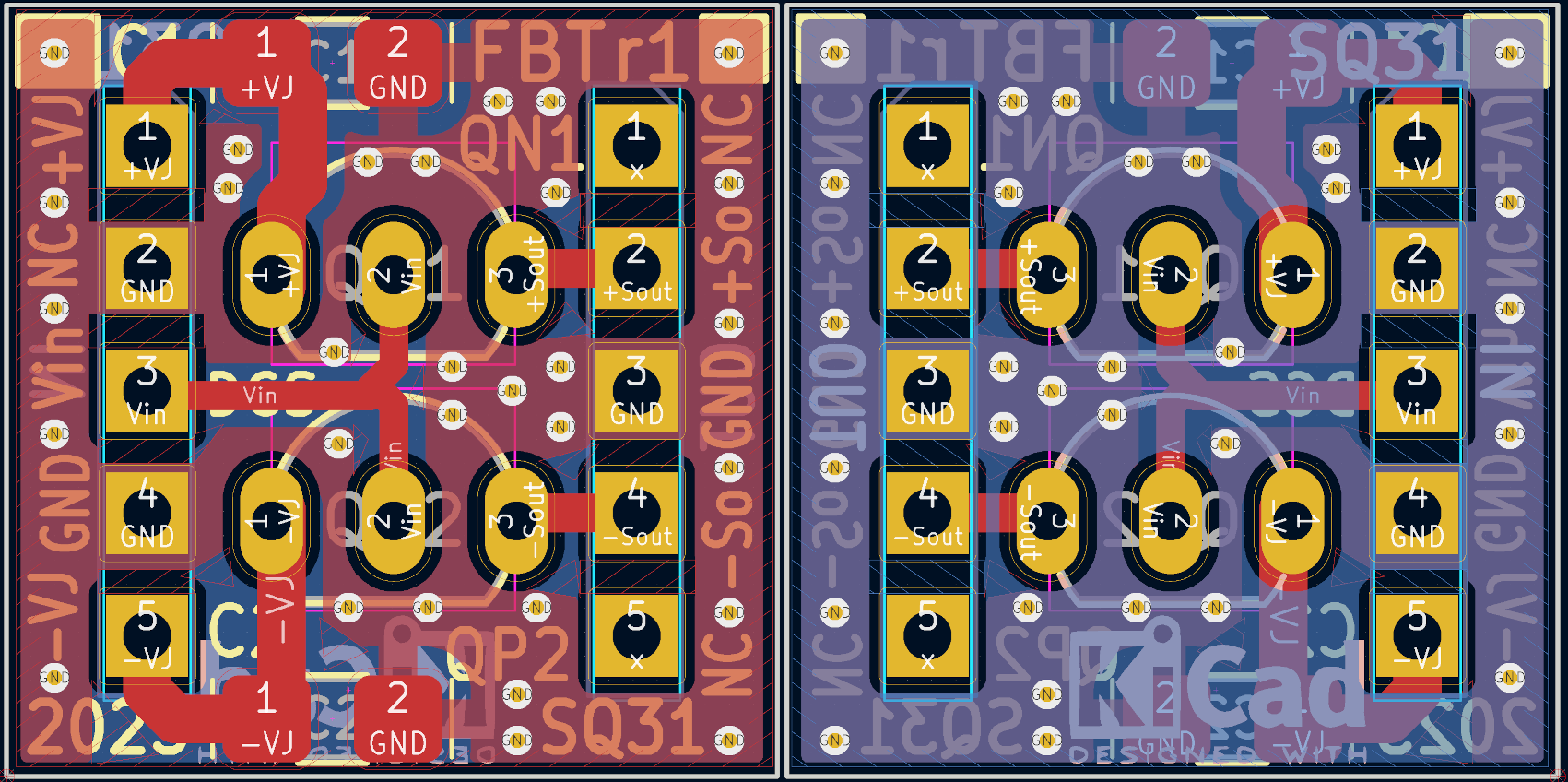

コンポーネント:FBT (JFET 簡易バッファ基板・スルーホール版 v1)

概要

手持ちの 2SK170 / 2SJ74 を利用するための基板です。従来品やHBDとの音質比較用・検証用となります。

自分も昔にヘッドホンアンプとかで使っていた定番回路ですね、今では貴重なローノイズJFETですが何個かストックしていました。

設計

プリント基板は表裏2層です。表面実装コンデンサは予備ですが、使った場合は品種により出音も変わるかもしれません。

計測結果の比較は後述します。

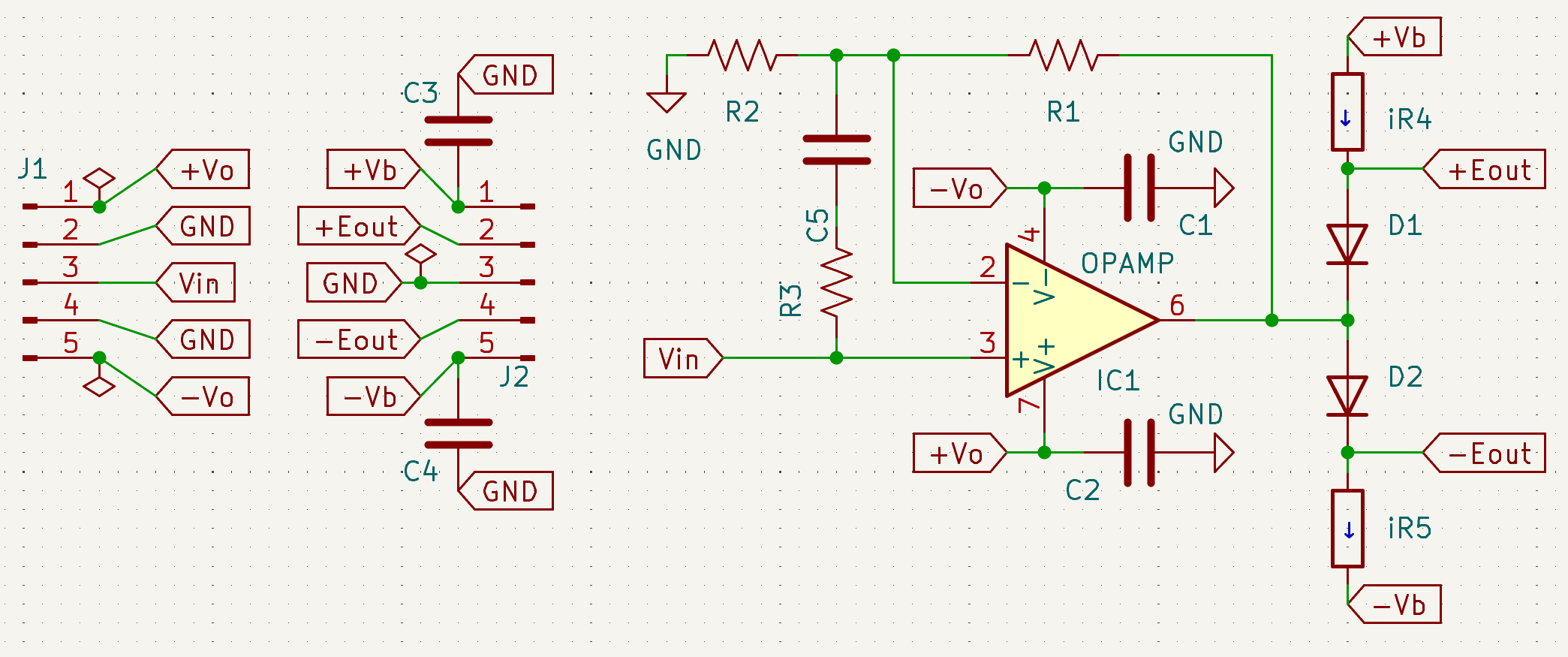

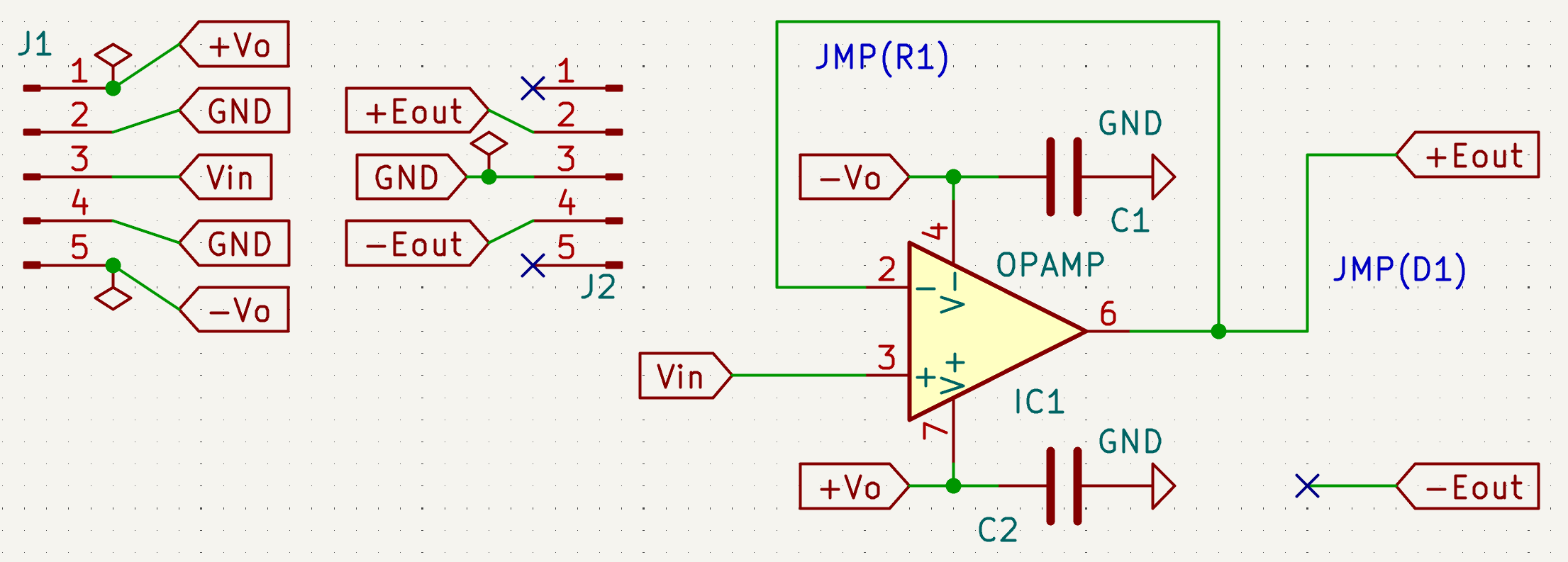

コンポーネント:OPBC-A / OPBC-B (オペアンプ簡易バッファ基板 v1)

概要

前述バッファ HBD が余りにも複雑なバッファ回路となってしまったため、オペアンプのみの簡素なバッファを比較のため急遽作成しました。

ボルテージフォロアとして使いますが不安定な場合もあるのでプリント基板には複数の調整余地を含めました。

本モジュールはプリアンプ基板等で使いますが、OPBC-Bは出力BJTエミッタフォロアを駆動する場合専用、OPBC-Aはそれ以外の入出力バッファ用です。

基板自体が A・B 両用途で使えるようにしています。

設計

プリント基板は表裏2層で配線は済ませています。ジャンパ・抵抗・ダイオードなど使い方により部品が変わります。

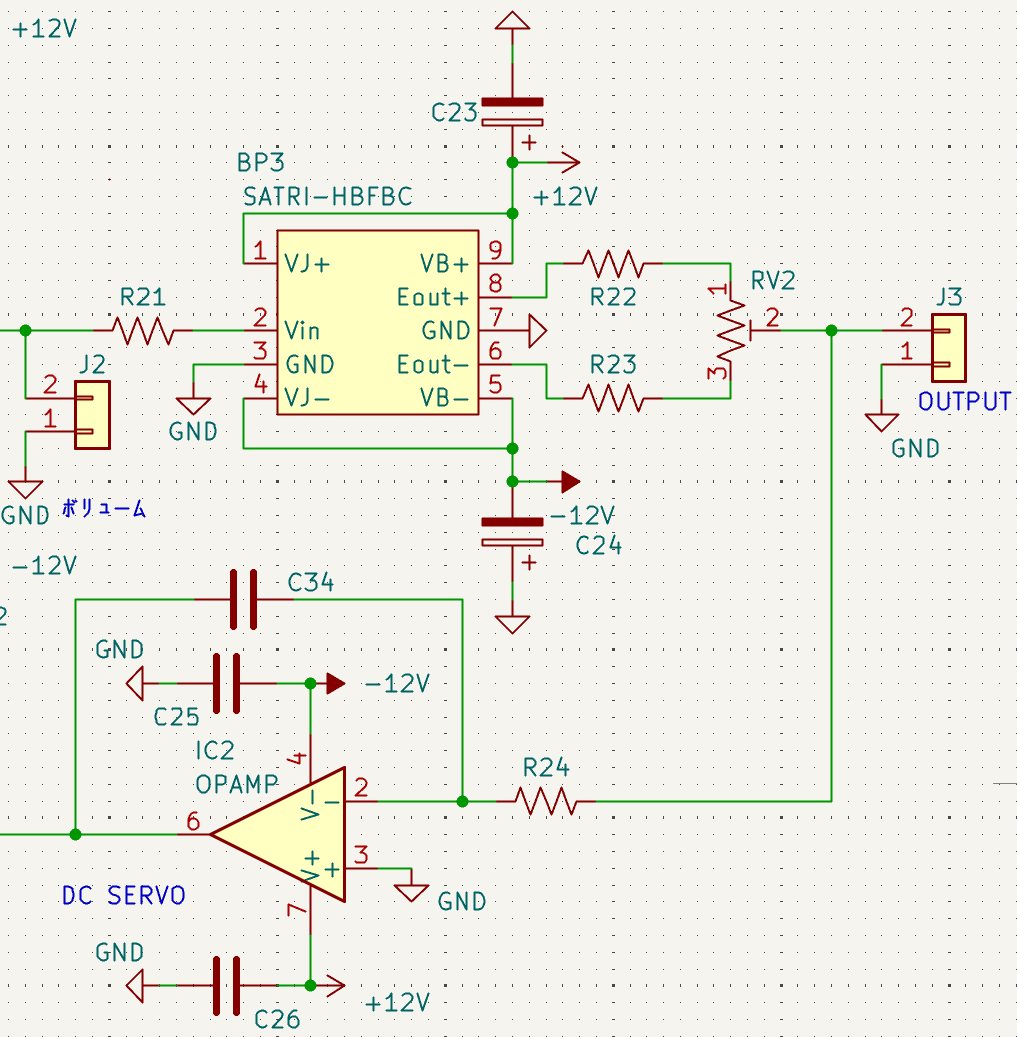

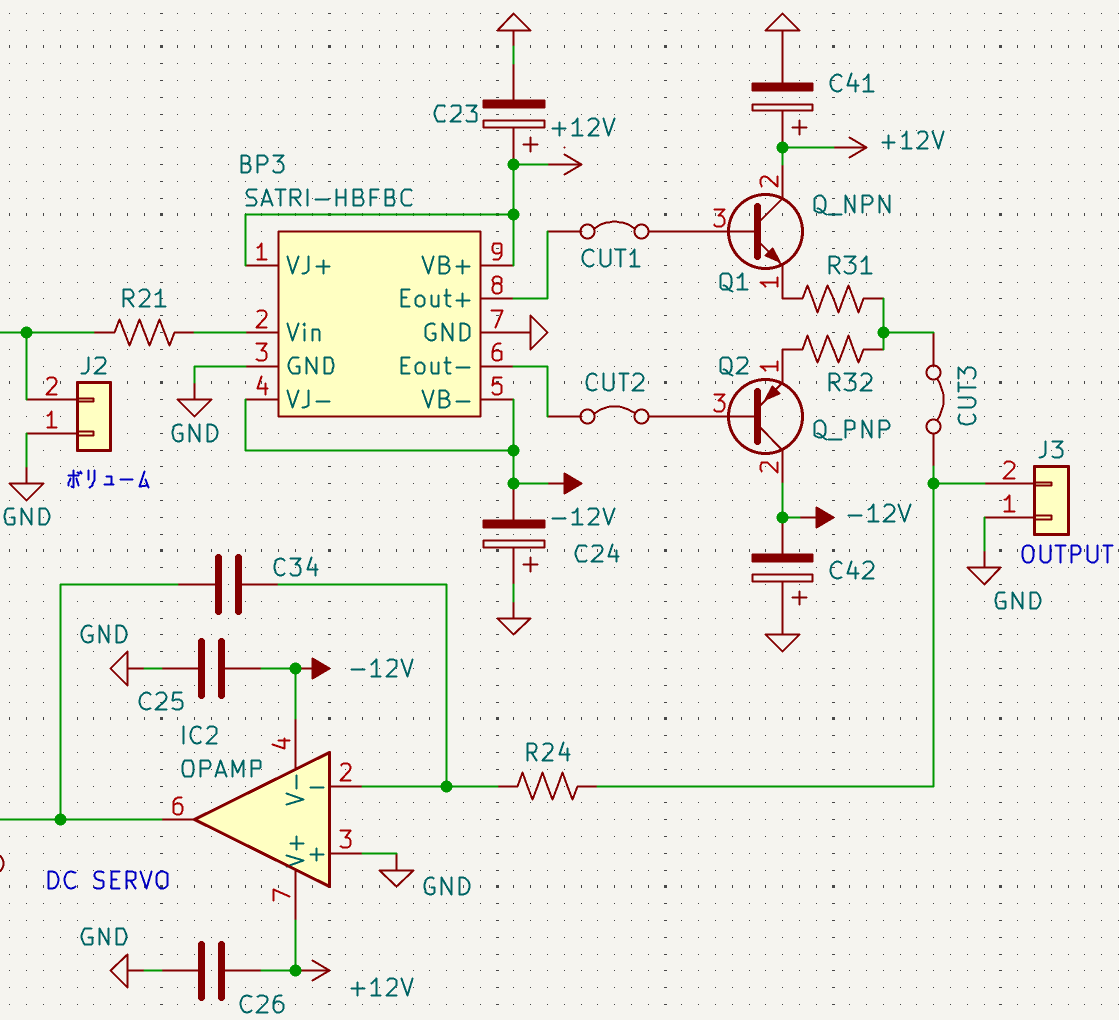

モジュール利用例:入出力バッファ(OPBC-A)、および適用出力バッファ例

モジュール利用例:出力BJTエミッタフォロア駆動専用(OPBC-B)、および適用出力バッファ例

計測

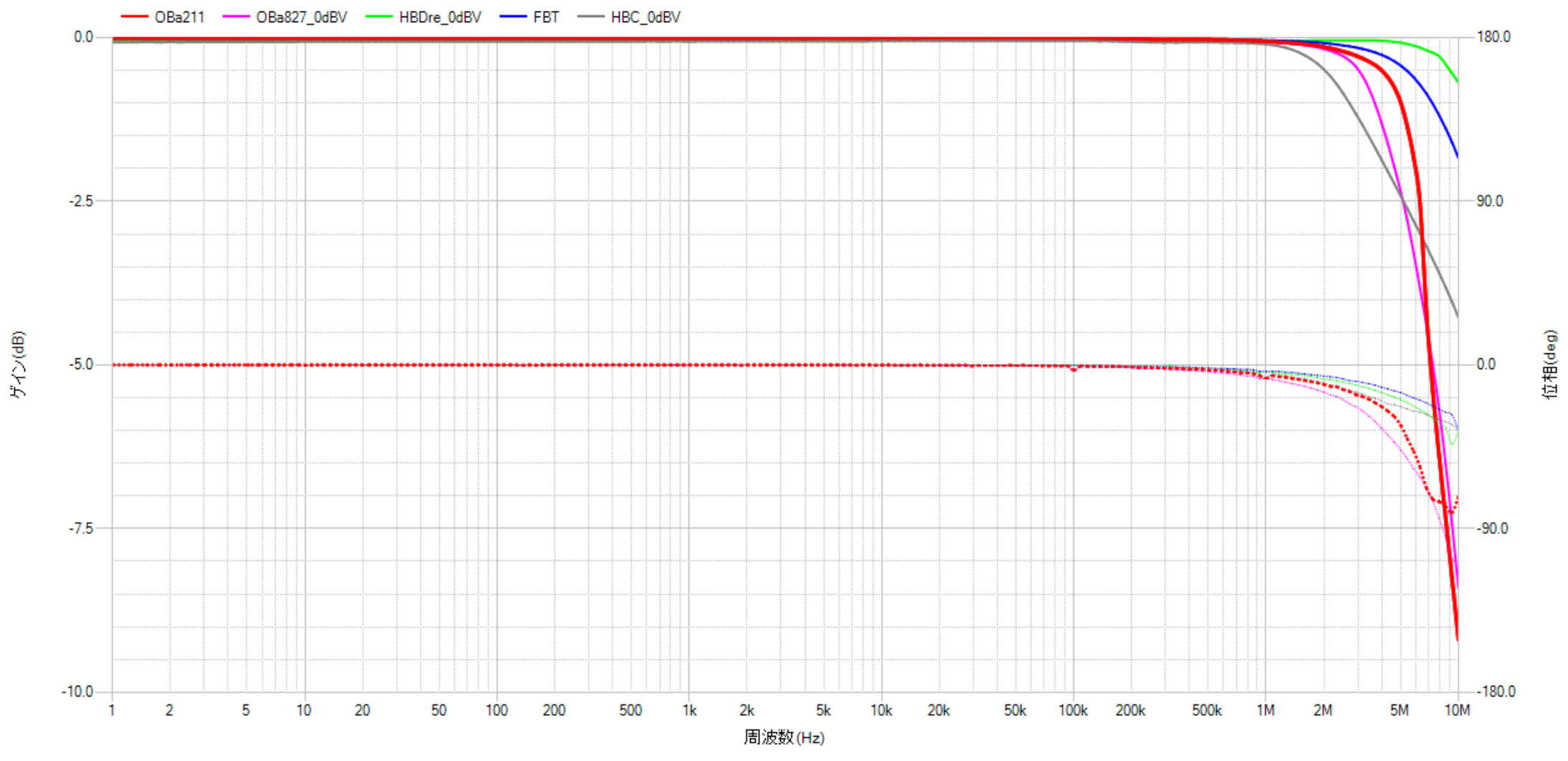

計測ツール(Analog Discovery2 + 自作テスト基板 + ソフトFRAplus)で評価してみます。

まず100kHz超までフラットでありバッファとしてはとりあえず問題無いと感じます。

グラフを拡大します。TI OPA211(グラフ赤色)、TI OPA827(グラフ紫色)はほぼほぼ同じでした。

そして過去の定番 2SK170/2SJ74ソースフォロア(グラフ青色)も悪くないのですね。

HDBv2(グラフ緑色)が伸びているのは嬉しいですね。

計測ツールでは歪率については周波数別と出力別で計測出来ます。

10KHz以上は恐らく計測パラメータ設定が上手くいっていないと思われます。

評価方法も難しいけど計測方法も難しいです。

入力バッファとしてはボルテージフォロア(G=1)安定のオペアンプであればBJT/FETタイプいずれでも大丈夫だと思いますが、 プリアンプの出力バッファ(ボリュームの後に設置)はFET入力タイプが向いているため使い分けは留意する必要があります。