![]() 記事作成中 Under construction

記事作成中 Under construction

サブプロジェクトについて

はじめに

本サブプロジェクトは、リフローはんだ製造技術の習得、および、SATRI-ICピン配置ハイブリッドICモジュール製作を行います。

本モジュールは部品として各プロジェクトで利用します。

プリント基板のガーバーデータ、部品表などの製造資料等については

「設計データ頒布」に記載しています。

背景・目的

バクーンプロダクツ社 の多くの製品に組み込まれていた 電流入力 ハイブリッドICモジュール SATRI-IC ( サトリIC )。 これまで V4.1、 V4.2、 V4.3、 SP、 EX、 UL の6種類が登場しており、今は最上位品のULのみ継続販売されています。 比較的手ごろだった SATRI-IC-SP は販売終了、 SATRI-IC-EX も完売後に再生産されておらず、 残っている SATRI-IC-UL は大変高額なこともあり気軽に使えない状況です。 色々なアプリケーション回路を設計・検証する上では手軽に使えるエントリー版が欲しい状況です。

そんな折、入力バッファ HBD の製造にて 小型トランジスタ SOT363-6 サイズ(ピッチ0.65mm)という極小部品の大量実装に大変苦戦しました。 そのうえ手作業ハンダ付けを行ったバッファ・モジュールは大半が一発動作せず、修正作業にも時間を要しました。 作業時間を要した上に散々な品質実績であったこともあり、 電子工作の製造技術を抜本的に改善するため『 自宅リフローはんだ 』の製造技術導入が不可避だと悟りました。

極小部品 SOT363-6 を大量に実装するリフロー習作としては

SATRI ICピン配置ハイブリッドIC が丁度イイのではないか?!と思い当たりました。

手段が目的の本サブプロジェクトですが、収穫が多いサブプロジェクトとなりました。

留意点

- 工具については、別ページ「工具について」にまとめました。

- 本記事ではSATRI-ICの詳細な使い方は記載しておりません。使用方法・設計方法は、 バクーンプロダクツ社にて公開されている資料 「 SATRI-IC技術マニュアル (SATRI IC technical manual)」、 「 SATRI-ICアプリケーション設計ガイド (SATRI IC APPLICATION DESIGN GUIDE)」等を参照するようにしてください。

- ハイブリッドIC は SATRI-ICピン配置 として設計していますが、完全な互換性は保証しておりません。

- 既存のSATRI-ICと本サブプロジェクト品を差し替える場合、問題が発生することがあります(耐圧・許容損失オーバー、発振)。

特に2011年より前に販売されていたSATRI-IC V4.1 ~ V4.3 および SP と交換しただけでは恐らく発振します。最悪、機器やスピーカーを破損する可能性があります。アンプ回路の事前対策が必須です。

概要:SATRI-ICについて

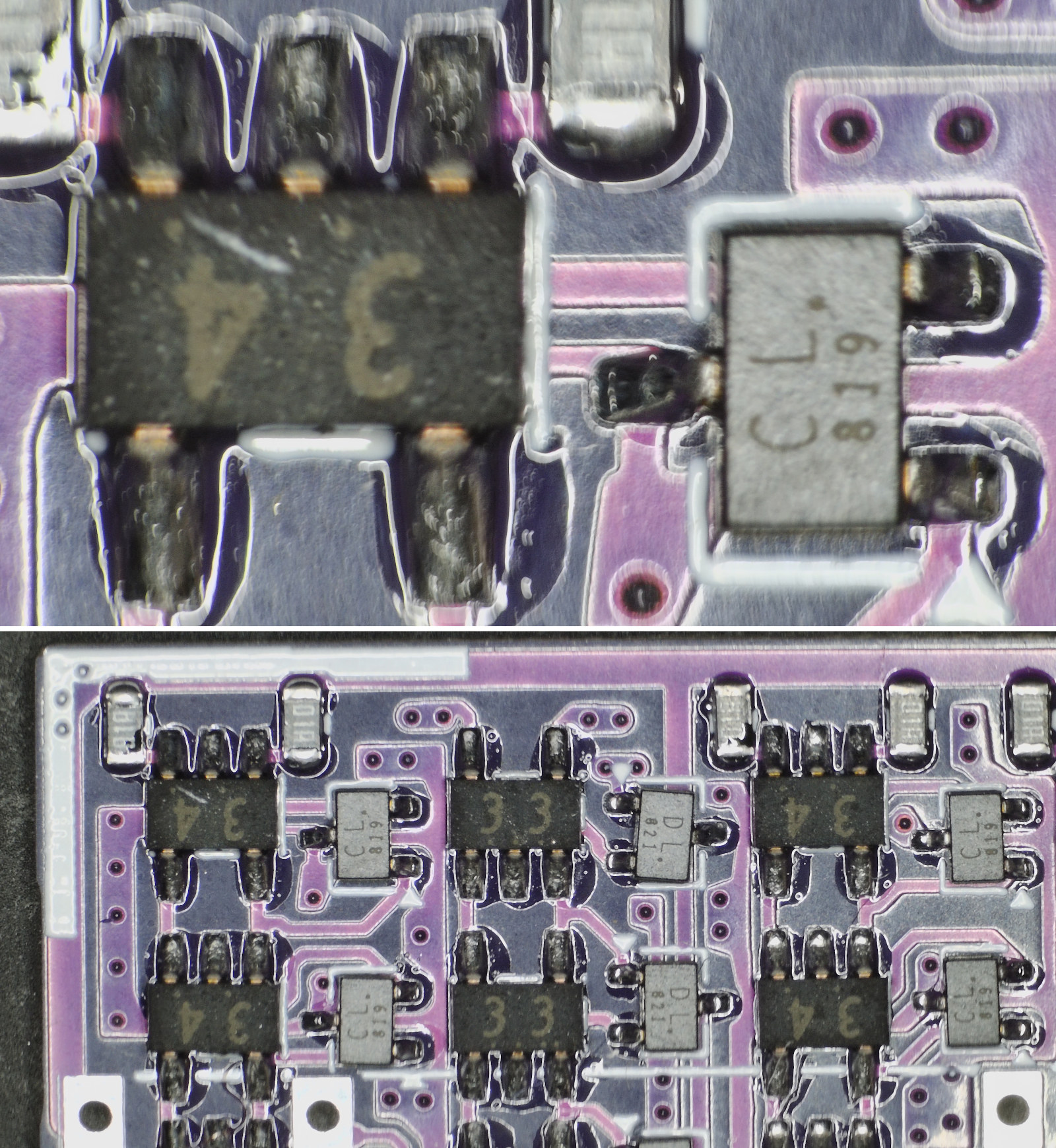

写真:SATRI-IC 製品

販売されていた SATRI-IC の写真です。

写真:左、緑色のハイブリッドICはトランジスタ(BJT) 32個で構成されたV4回路でして、

左上からV4.1、V4.2、V4.3です。基板が片面 -> 両面 -> メッシュGNDと進化しており、

表面実装トランジスタや抵抗についても低雑音・高精度品に見直しされているようです。

写真:右上(黒色)はV4の次に発売された SATRI-IC-SP v1.0 (スーパープレシジョン(BJT 44個))、

写真:右中段(紫色)は最新・現行品・最上位品の SATRI-IC-UL v1.0 (アルティメイト(BJT 72個))です。

なお個人的にはULと同時期に併売されていた赤色の SATRI-IC-EX (エクストラ(BJT 48個))は持っていません。

ULとEXはより小さなトランジスタを使用して集積度が上がっており、更にmatched dual BJTが使われており高精度化も行われています。

(使われているBJTは恐らく SPはRohm IMX1/IMT1A ?、ULはNexperia BCM847BV/BCM857BV ?)

SATRI-ICと合わせて使うオプション基板モジュールも別にありました。

写真の上段は「 SATRI-IC V5.1 」という定電流ダイオード(CRD)をバイアス電流源とするときに使う電流源安定化回路、

写真の下段はIC用ソケット「SATRI-IC-Socket」(兼グランドプレーンノイズ低減)です。

このV5.1はCRDにかかる電圧がブレないようにするスタビライザー回路だったのですが現行製品では使われていません。

現在はより安定度が高いLM334がバイアス電流源として使われています。

カレントコンベア回路について / CCII

SATRI-IC と呼ばれているこの ハイブリッドIC、

初期世代は SATRI V4回路 と呼ばれていたと記憶しています。

トランジスタを32個~72個集積したモジュールとなっています。

一般的にはなんと呼称すればよいのか未だに自分でもよく分かっていません。

各プロジェクトではハイブリッドICと呼びますが、

設計したモジュールは複数あるので厳密に区別するときは自作モジュール設計名称「SCCM-xx」と呼ぶこととします。

このモジュールで使われている回路ですが幾つかの文献だと Fabre-Normand translinear current conveyors という名称で知られているようです。 大きな分類としては Second Generation Current Conveyor / CCII という回路に分類されており、 入出力が電流であることから電流モードアンプとか、 出力インピーダンスが非常に高い電流源となるからトランスインピーダンス回路とか呼ばれているようです。 電圧入力/電流出力の面からトランスコンダクタンスアンプという側面もあります。 勉強不足の自分には正直良く分かりませんが、実際には色々と使われている回路のようです。

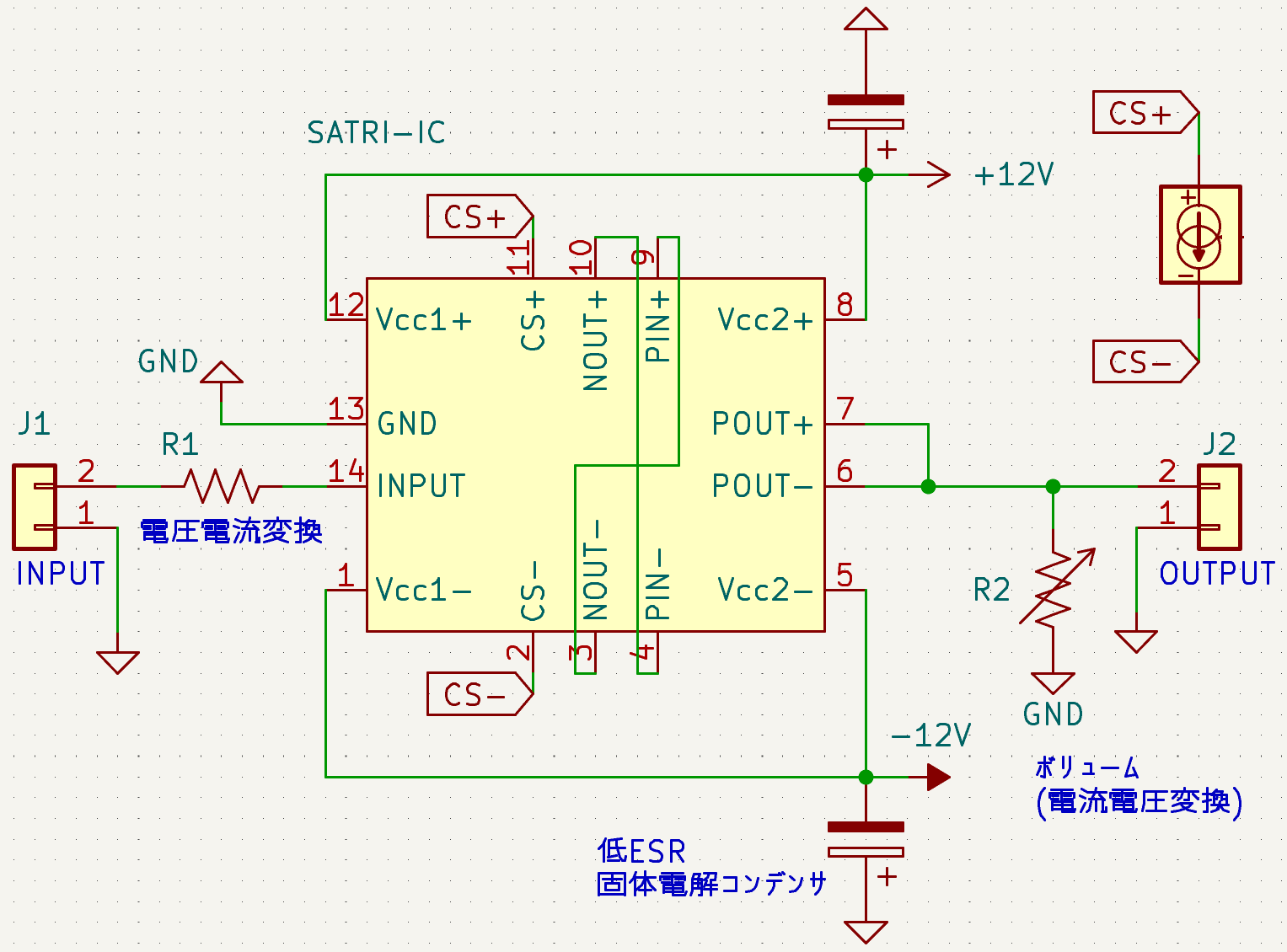

以下は説明用に簡素化した回路イメージです。

Fabre-NormandあるいはSATRI-ICがこの回路というわけではありません。

SATRI V4回路では電流入力にはinXを使うのですがoutZ+は反転出力となってしまいます。

再度カレントミラーで折り返してoutZ-にて非反転出力として信号を取り出せます。なおinYはGND接地します。

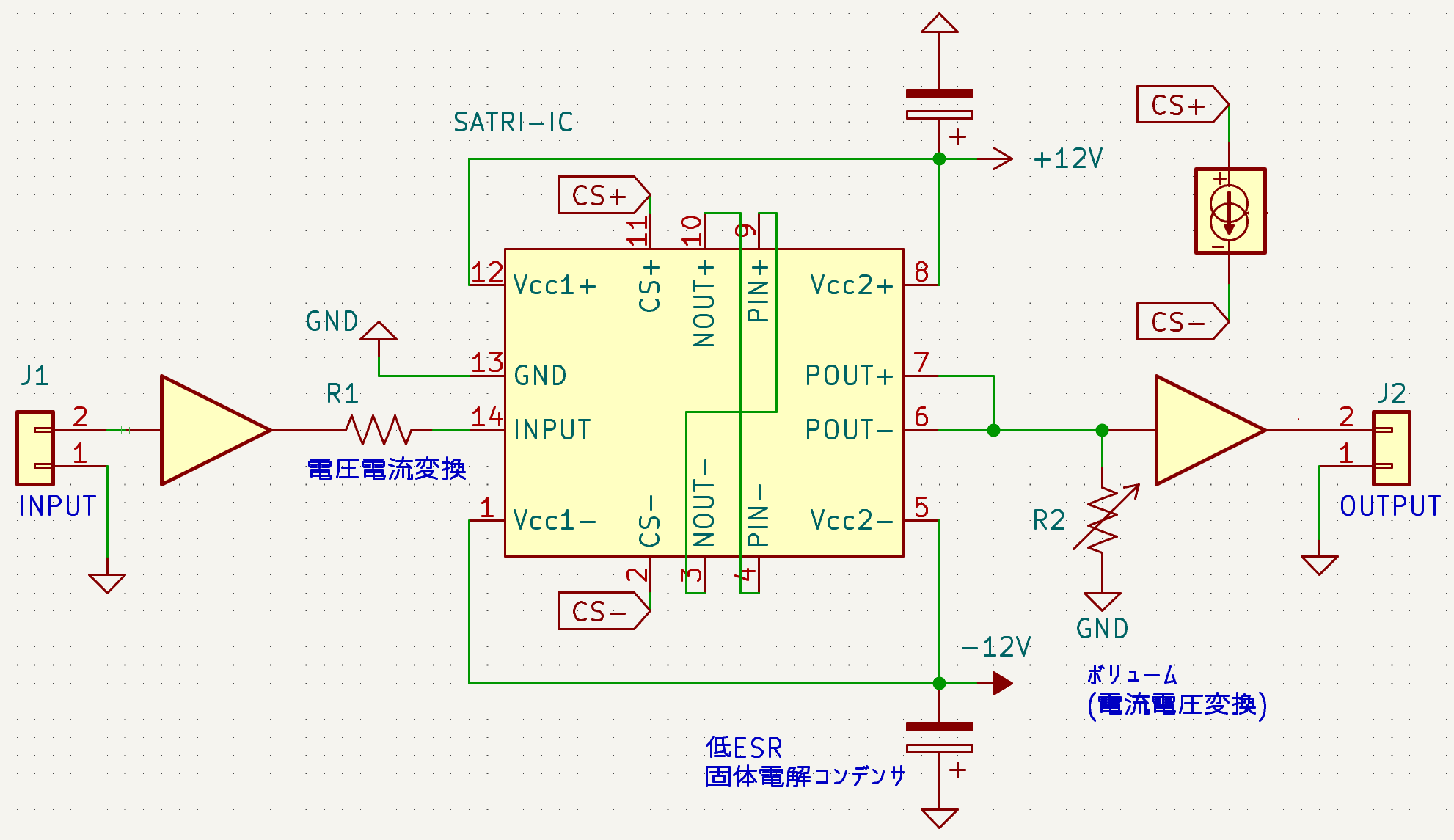

SATRI回路 での SATRI-IC 利用法

最小構成の使い方としては、正負電源(±12Vなど)、入力の電圧電流変換の抵抗R1、出力の電流電圧変換の抵抗R2、

および、ハイブリッドIC直近に低ESRな固体電解コンデンサを配置します。

バイアス電流源(CS)は定電流ダイオード [CRD:2mA~3mA]が適切ですが、

抵抗1本[電源電圧÷抵抗値]でも一応は動作します。

音量調整については R2 を可変抵抗とすると調整できます。

例えばスピーカーを駆動させるアンプでは

R1を1kΩ、R2を10kΩ・Aカーブのボリュームとすると音量調整することが可能となります。

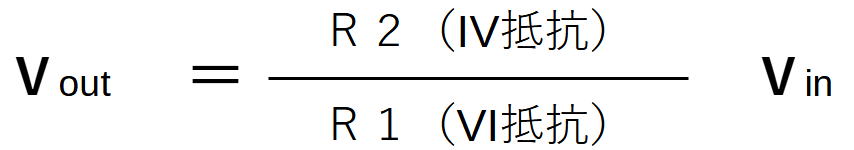

アンプの音量は抵抗により決まり、つまり抵抗比で増幅度が決まります。

とはいえ抵抗R1が小さすぎると過大な信号電流がハイブリッドICに流れる事になります。

通常設計ではハイブリッドICへの供給バイアス電流を2~3mAとしており、

この電流値以内に収まる信号電流にしないと少し歪んで音質劣化する可能性があります。

(※入力の電圧電流変換抵抗R1は、

例えば1kΩだと上流のDACなどの信号電圧はおおむね問題無い入力信号電流とすることができると思います。

音質的には出力の電流電圧変換抵抗R2は小さい方がノイズを押さえられて望ましいです。

ただR2に使用するAカーブ・ボリュームなどの(普段利用で)調整しやすい範囲もあり、

(ヘッドホンアンプなどでは)逆にR1を数kΩに大きくしてバランスをとることもあります。

さじ加減が難しいですが、音入力機器や抵抗部品定数や使い勝手etcによって適切なR1・R2は調整が必要だと思っていた方が安全です。)

実際のSATRIアンプ製品では、入力バッファを電圧電流変換抵抗の前に用意するアンプ回路構成が多いようです。

どのような音の入力ソース(機器)であっても歪み少なく電流変換できます。またJFET入力のためアンプの入力インピーダンス定数を高くすることが可能です。

また出力側にも同バッファを用意するとハイブリッドICと後段(パワーアンプなら出力段)の干渉を切ることができ、

この用途についてはSATRI V8回路と呼ばれていました。これもJFET入力でゲートに電流が流れない点の効果です。

これらのバッファの前後配置は、精度向上による音質向上を狙ったものだそうです。

コンポーネント:SCCM-LE v1 (電流入力 Hybrid-IC 簡易版)

概要

『 SCCM-LE 』はSATRI-ICピン配置のハイブリッドICモジュールです。

作業時期は着想 2023年8月 、詳細設計開始 2024年2月、音出し 2024年5月 です。

単体では信号増幅はできず、信号電流を入力して信号電流を出力するカレントコンベア機能があります。

手段が目的のサブプロジェクトですが、とはいえせっかく作るなら一工夫したいと考えていました。 ハイブリッドICであるSATRI-ICは、V4で32個、SPで44個、EXで48個、ULで72個のバイポーラトランジスタが集積されています。 リフローはんだ習作においてはV4と同様にBJT 32個とすることにしましたが、折角なので今までになかった回路構成にすることにしました。

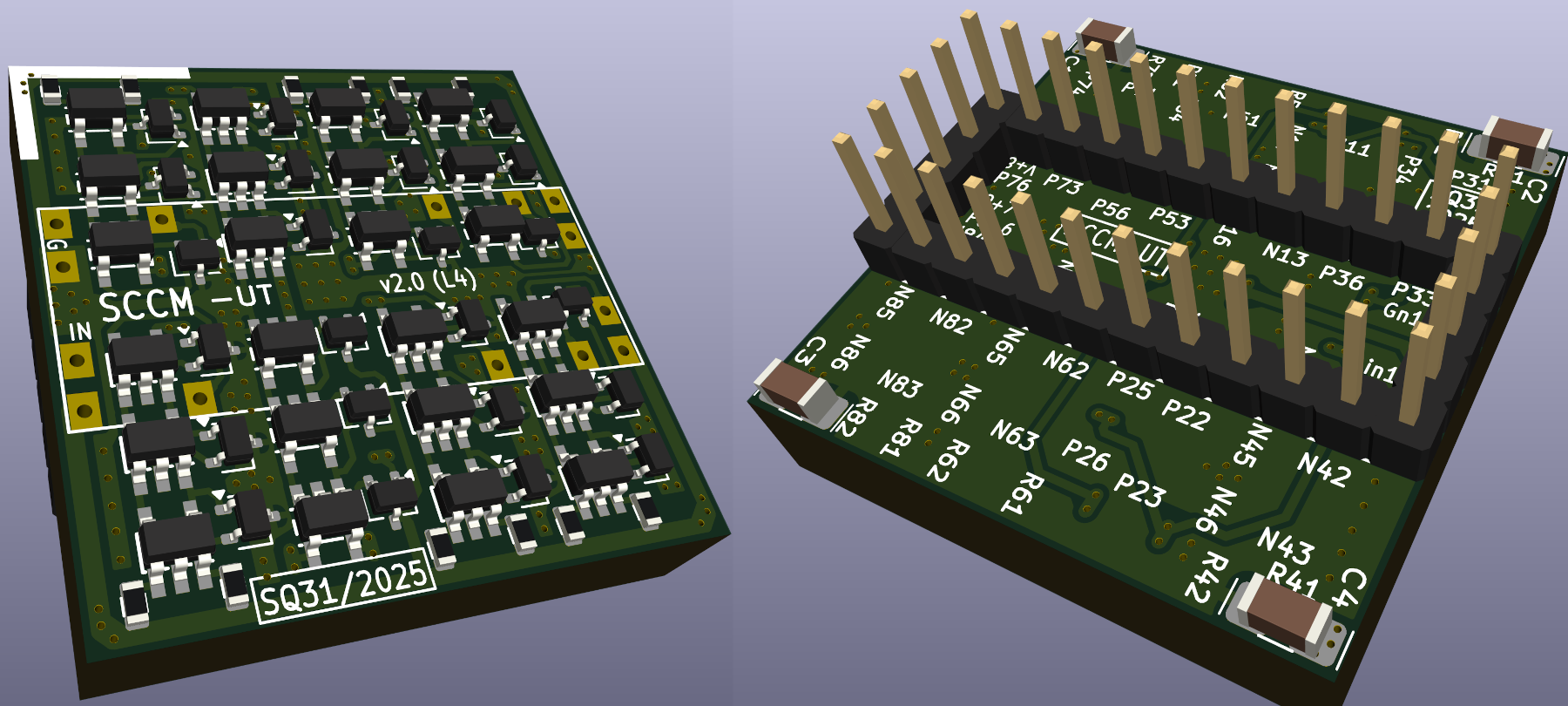

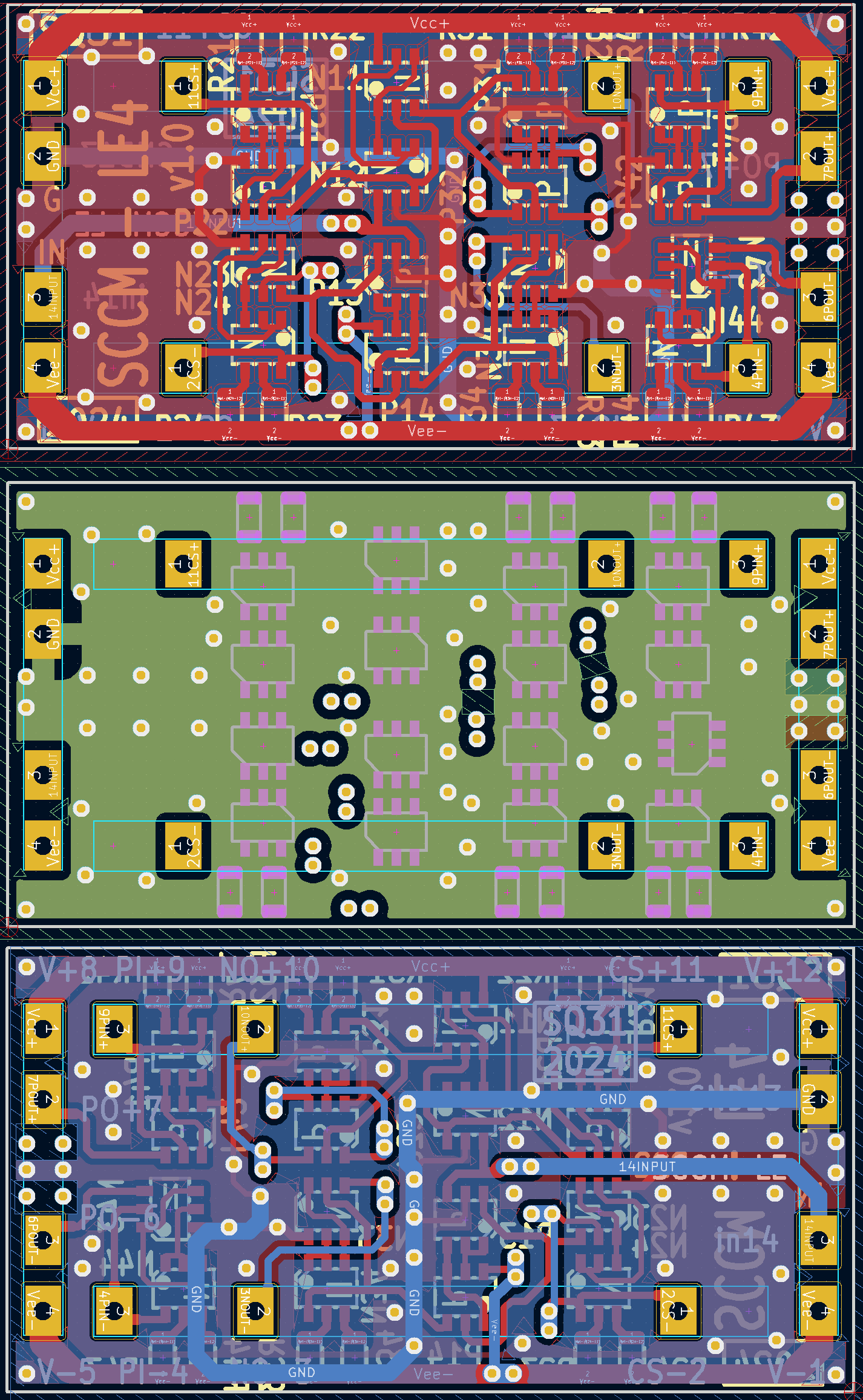

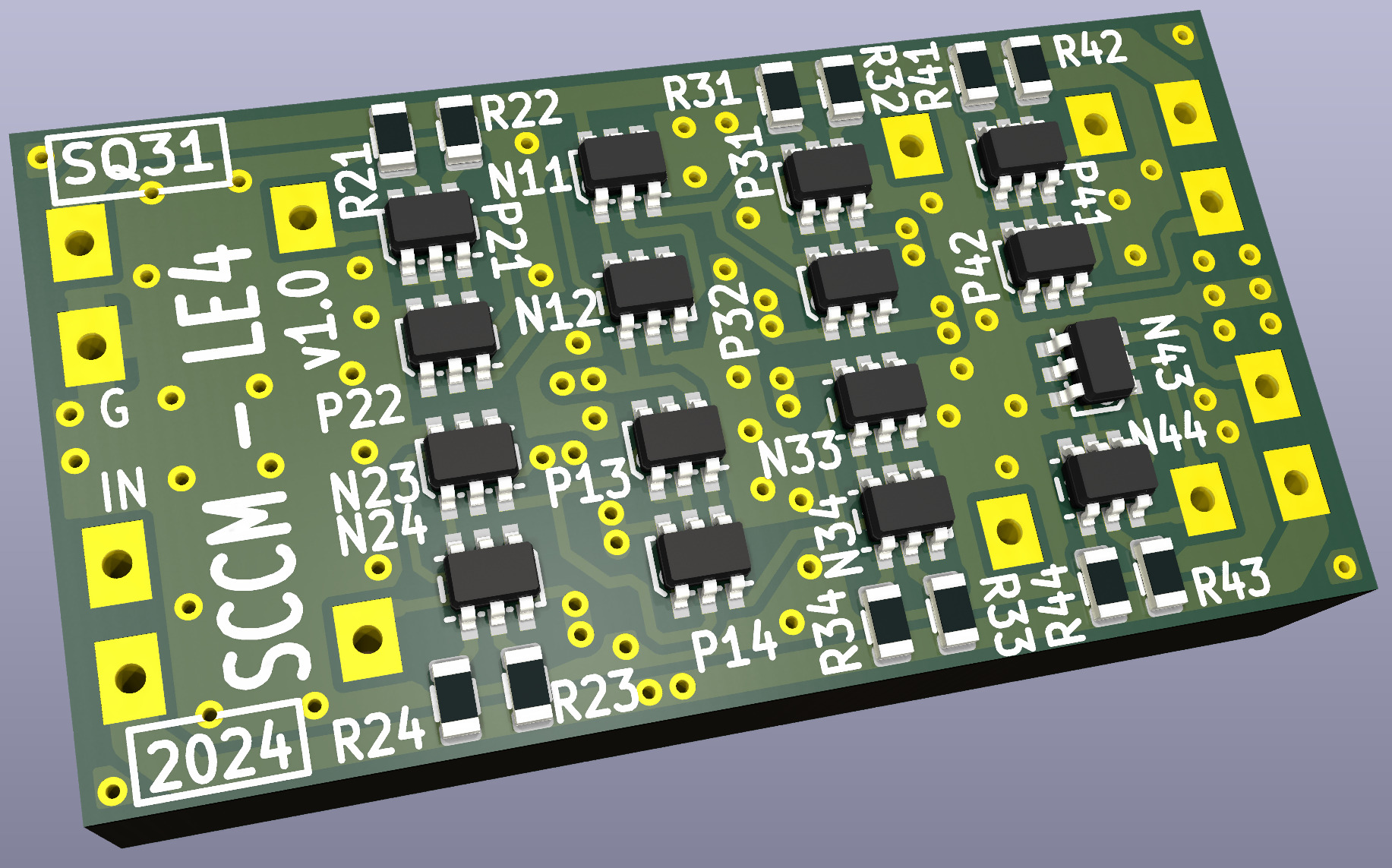

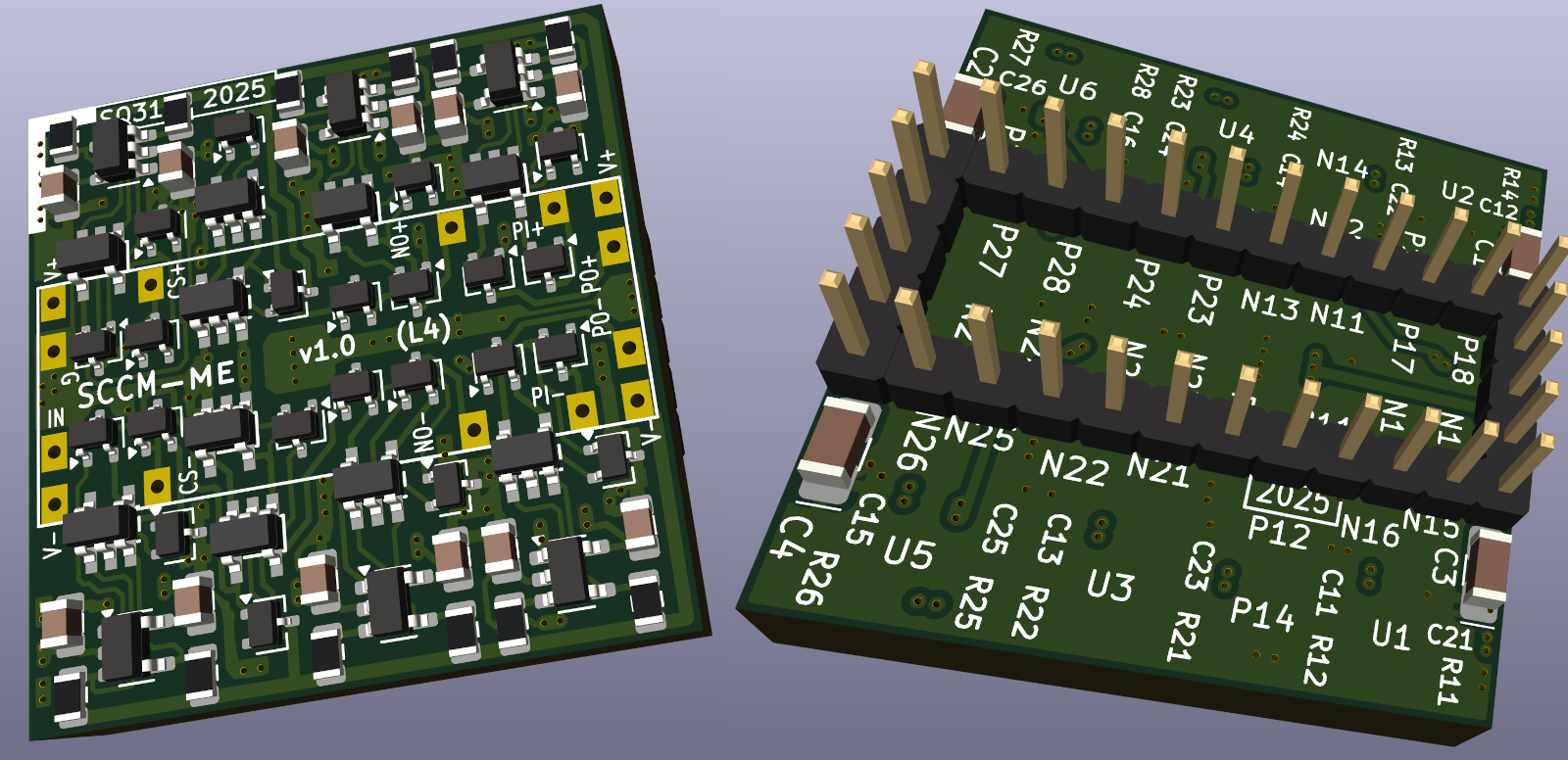

写真

SCCM-LE 全体の写真です。

自宅リフロー製造ということもあり、1回のリフローで済ませられるように半導体やチップ抵抗は表面側に全て集めています。

なお基板サイズですが、本家SATRI-ICは 30.5mm x 14mm なのですが、

本サブプロジェクトの SCCM-LE は短辺が少し長くて 30.5mm x 16mm としています。

理由としては無理のない設計とするため基板面積に余裕持たせたのもあるのですが、(中国の)格安プリント基板製造のデザインルールに15mm未満は増額になる所がありそれを意識したものです。

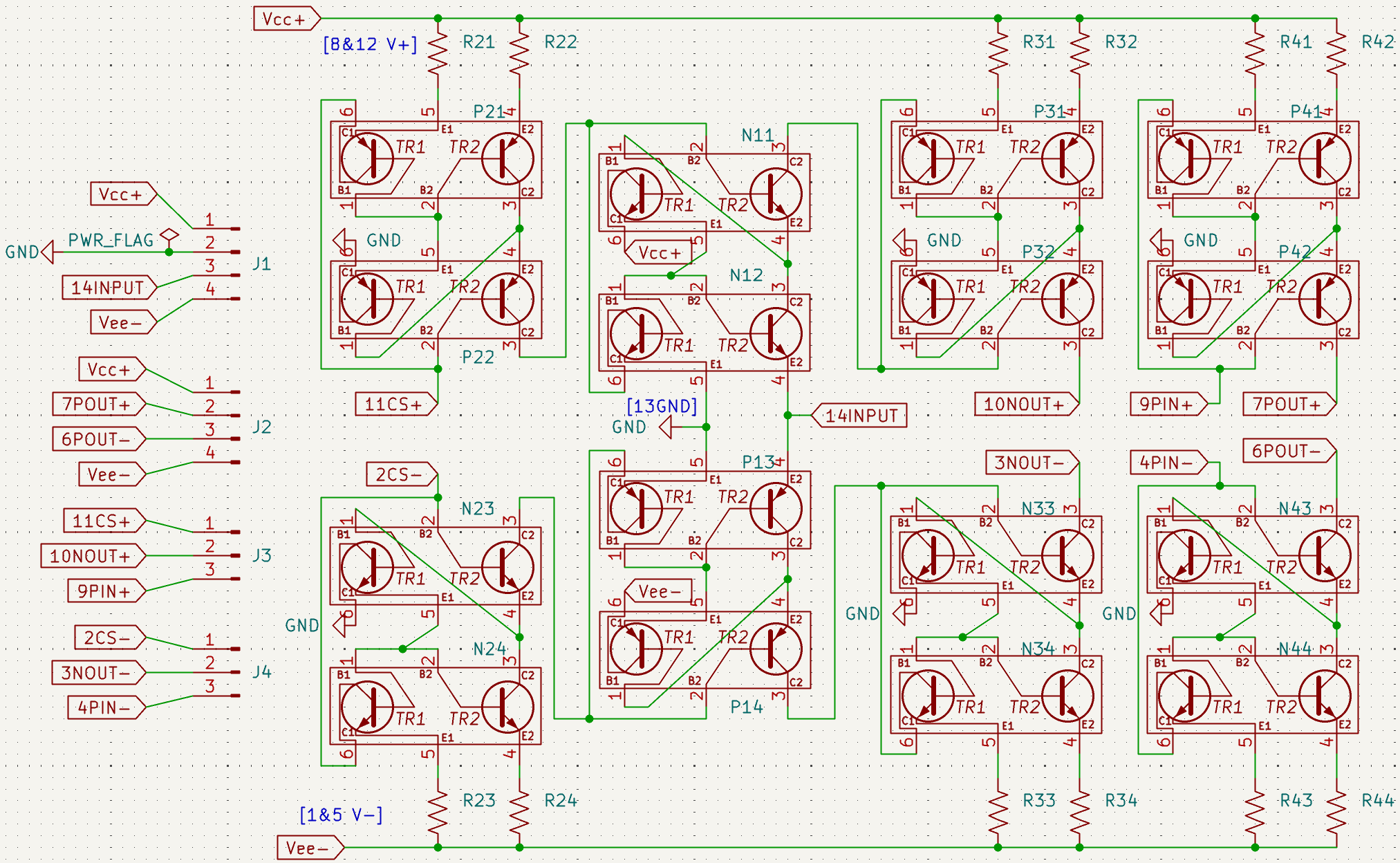

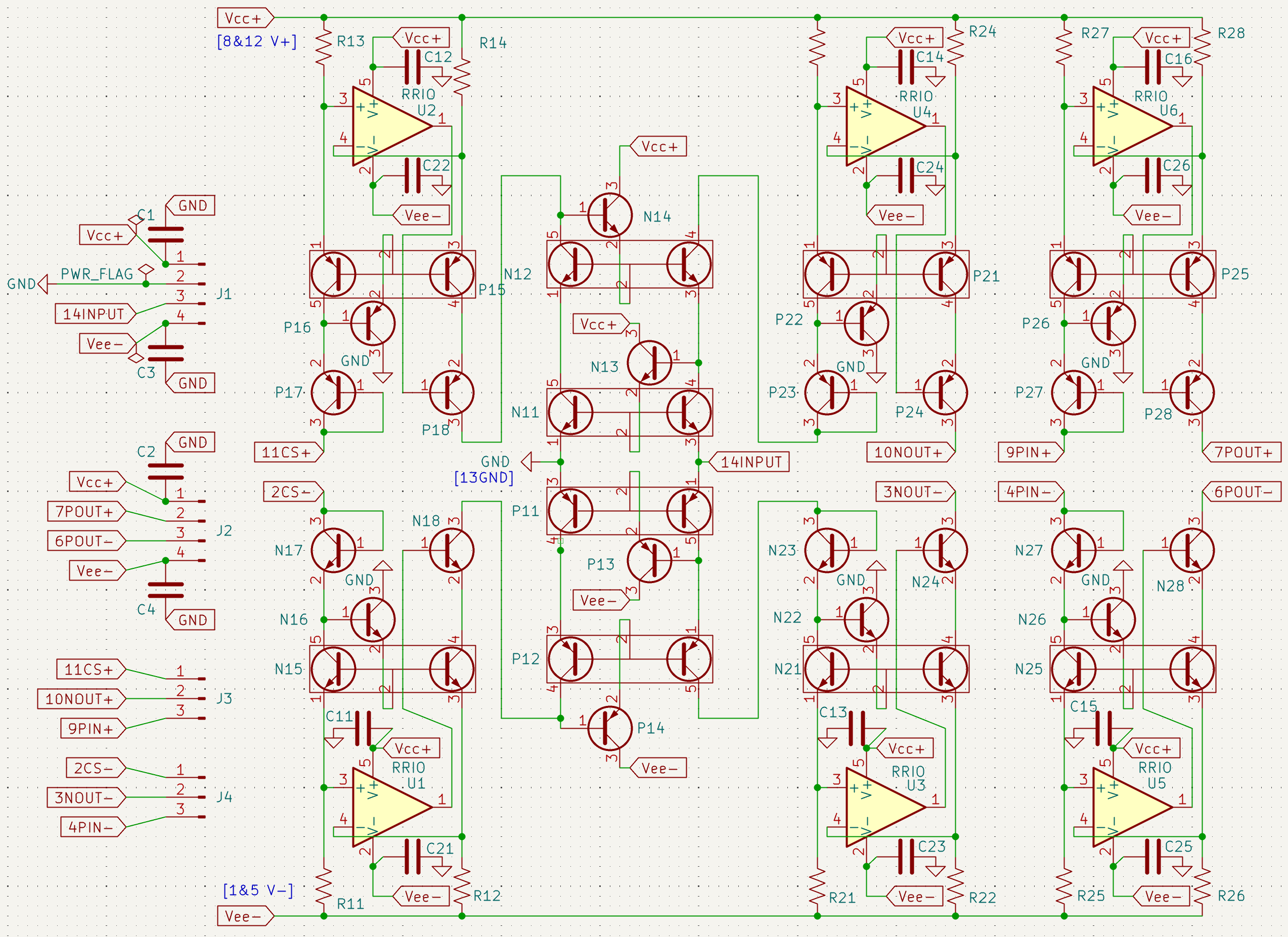

回路図

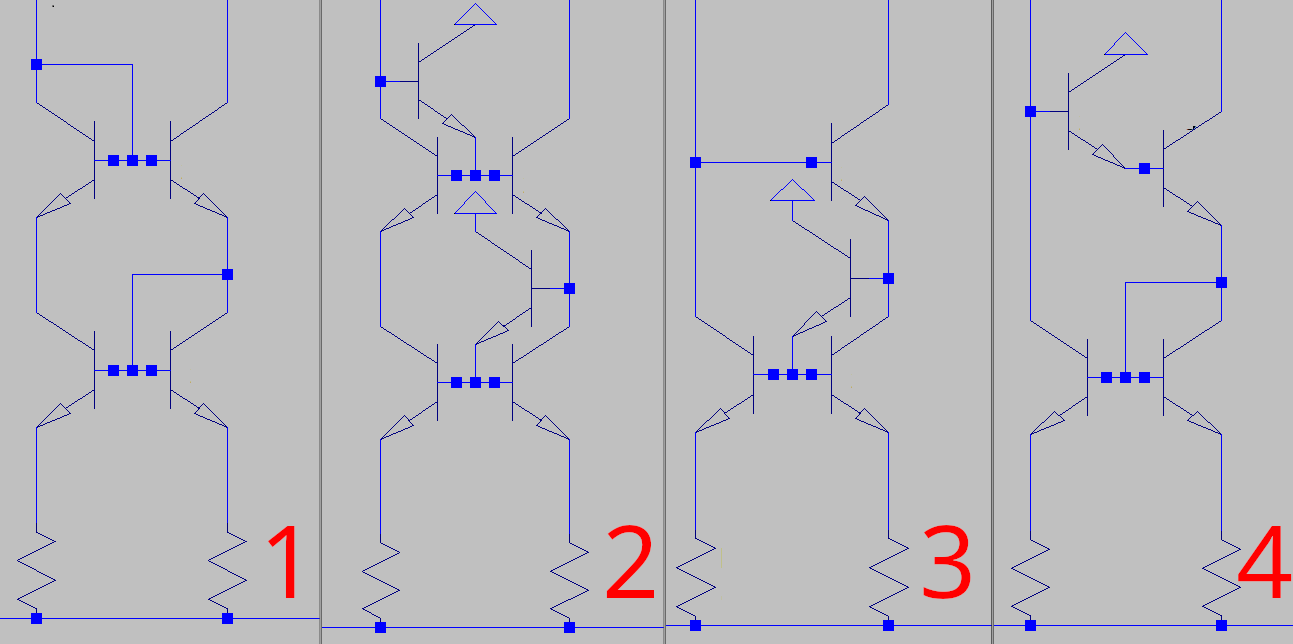

ハイブリッドIC は 8個のカレントミラー を組み合わせて構成されています(8ブロック構成)。

ここでカレントミラー回路は最小構成だと バイポーラトランジスタ2個 から構成できます。

SATRI V4回路ではトランジスタ4個から構成する『1:高精度ウィルソン 』(図の左端)が使われています。

今回は 高精度ウイルソン以外のカレントミラー についても比較検討してみることにしました。

ハイブリッドIC回路案についてはLTspiceシミュレーションで検討を重ねます。

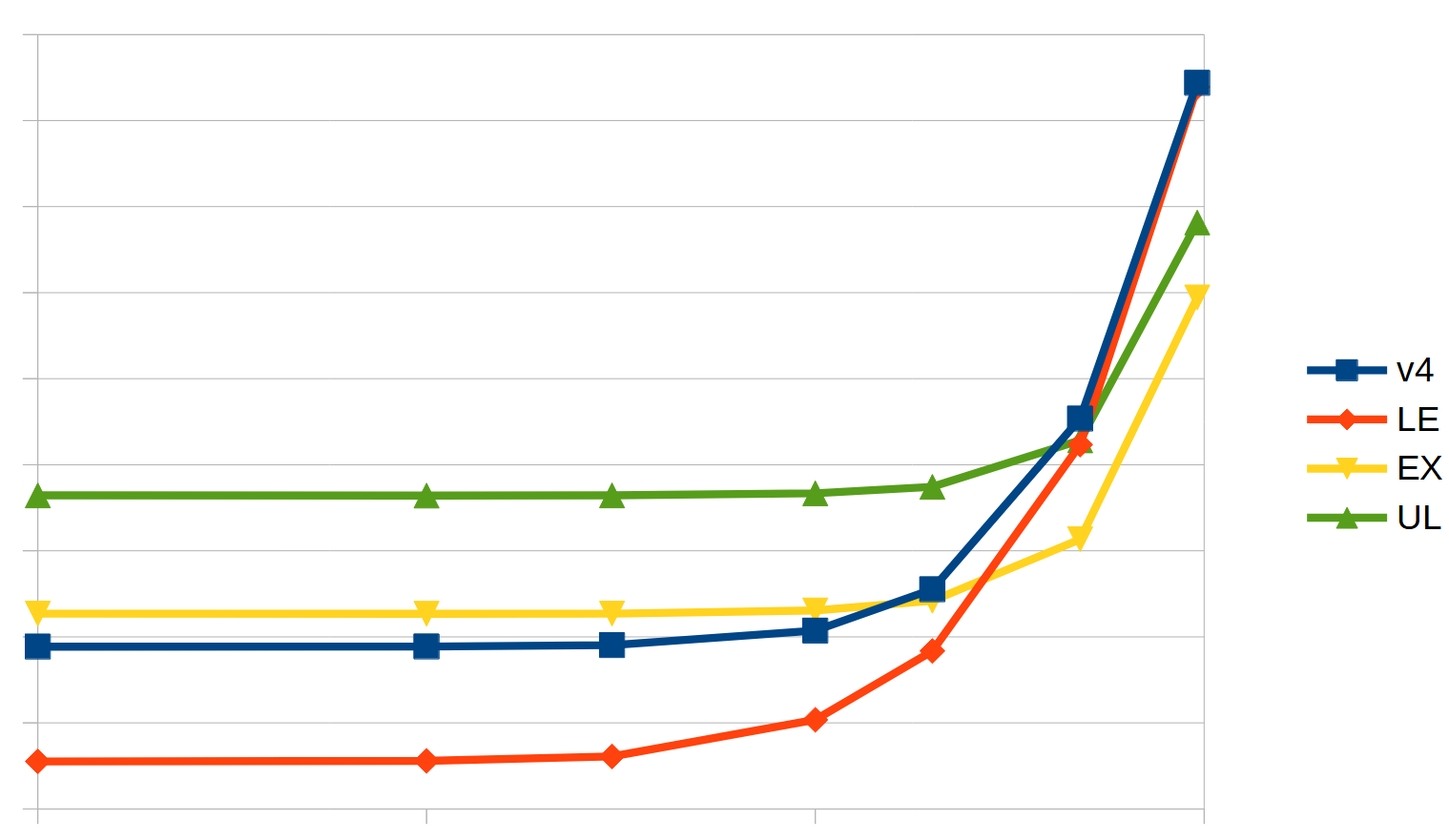

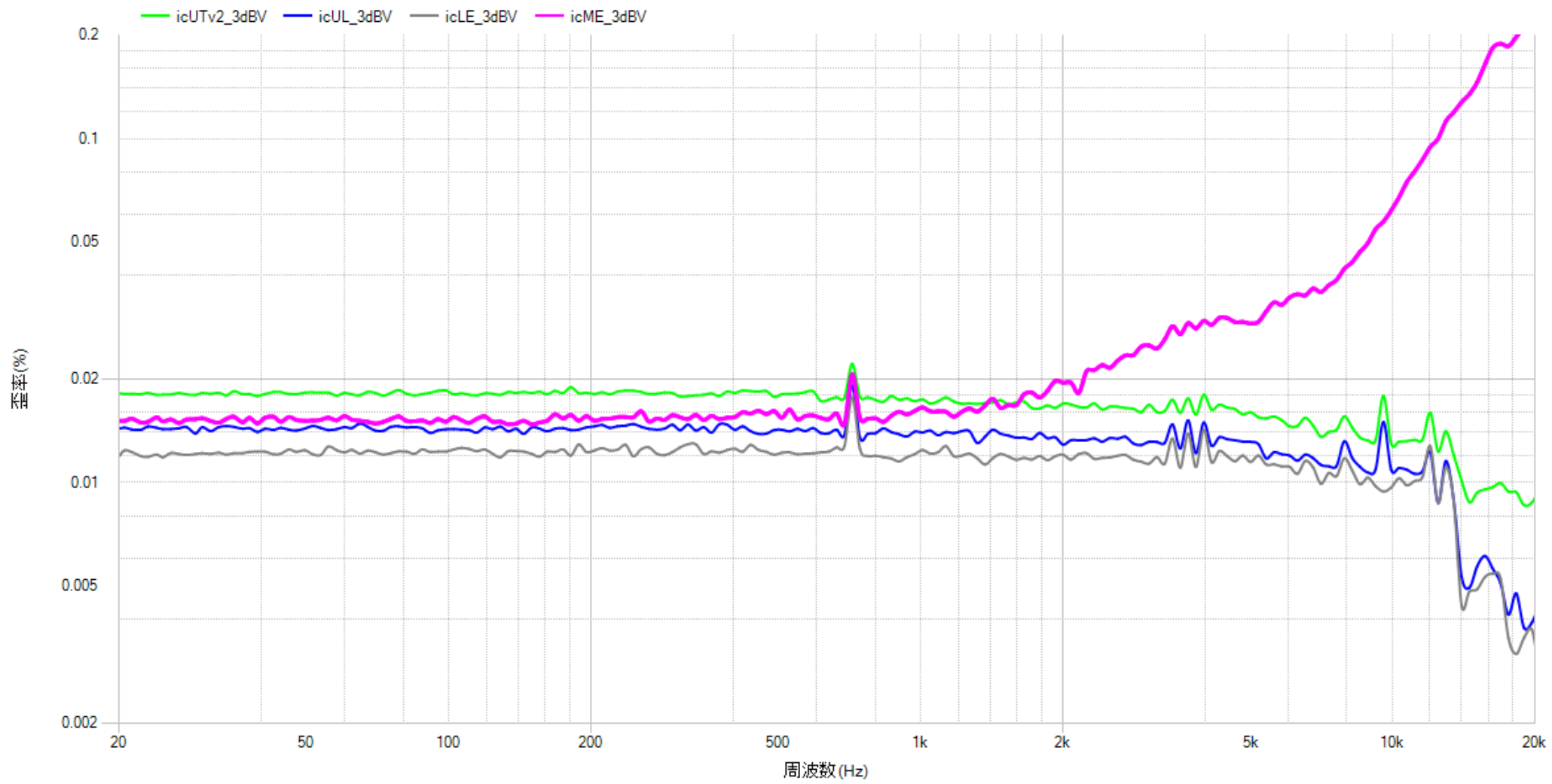

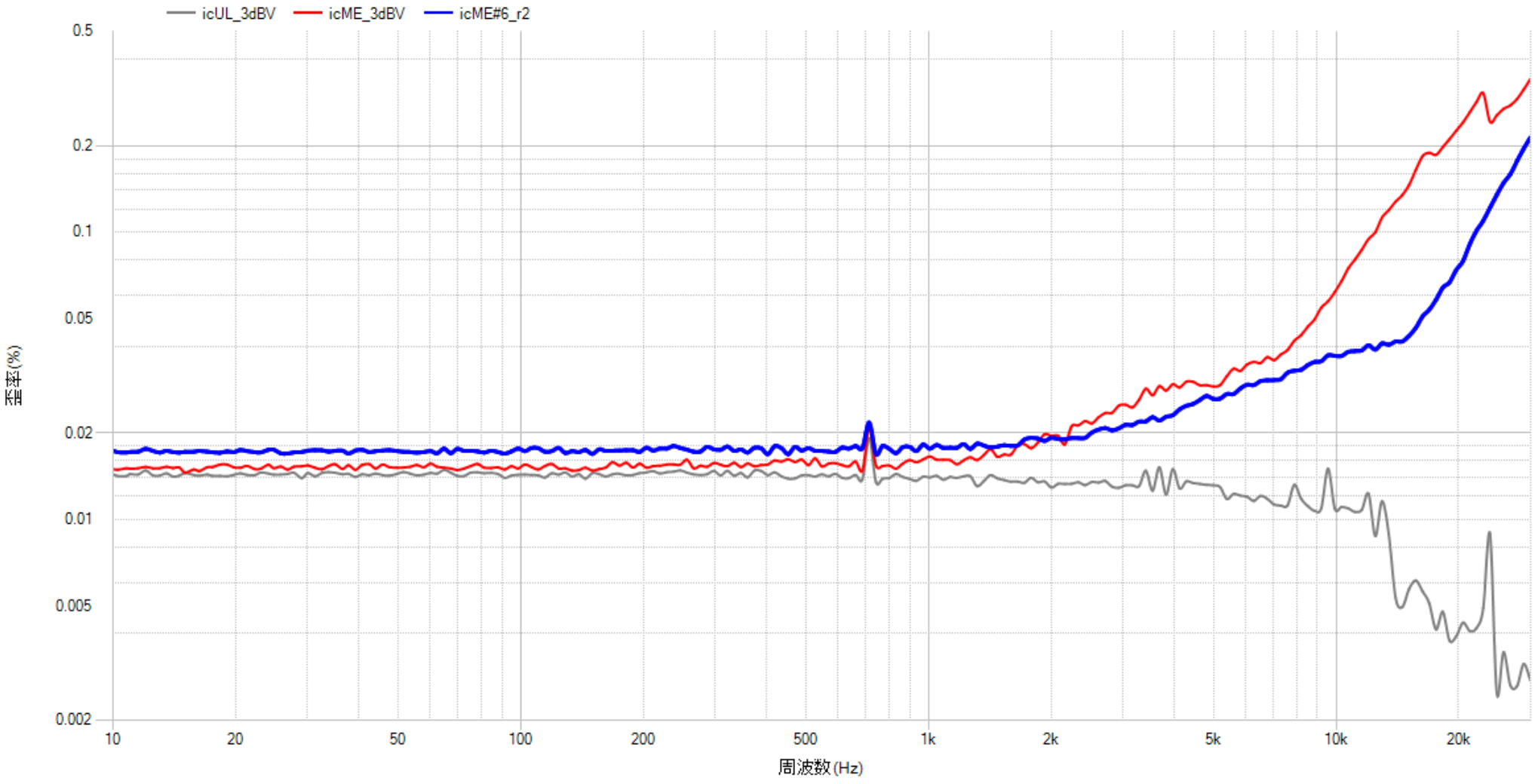

カレントミラー回路アイデア別に、横軸に入力信号周波数、縦軸に歪み率をグラフプロットして比較検討しました。

それぞれの詳細は割愛しますが、グラフ「LE案」は最小構成ですが良いシミュレーション結果が得られました。

SCCM-LEは『3: ウィルソンミラー(BJT x3個) に ベース電流補償 を1個加えた4個のトランジスタ』で構成しています。

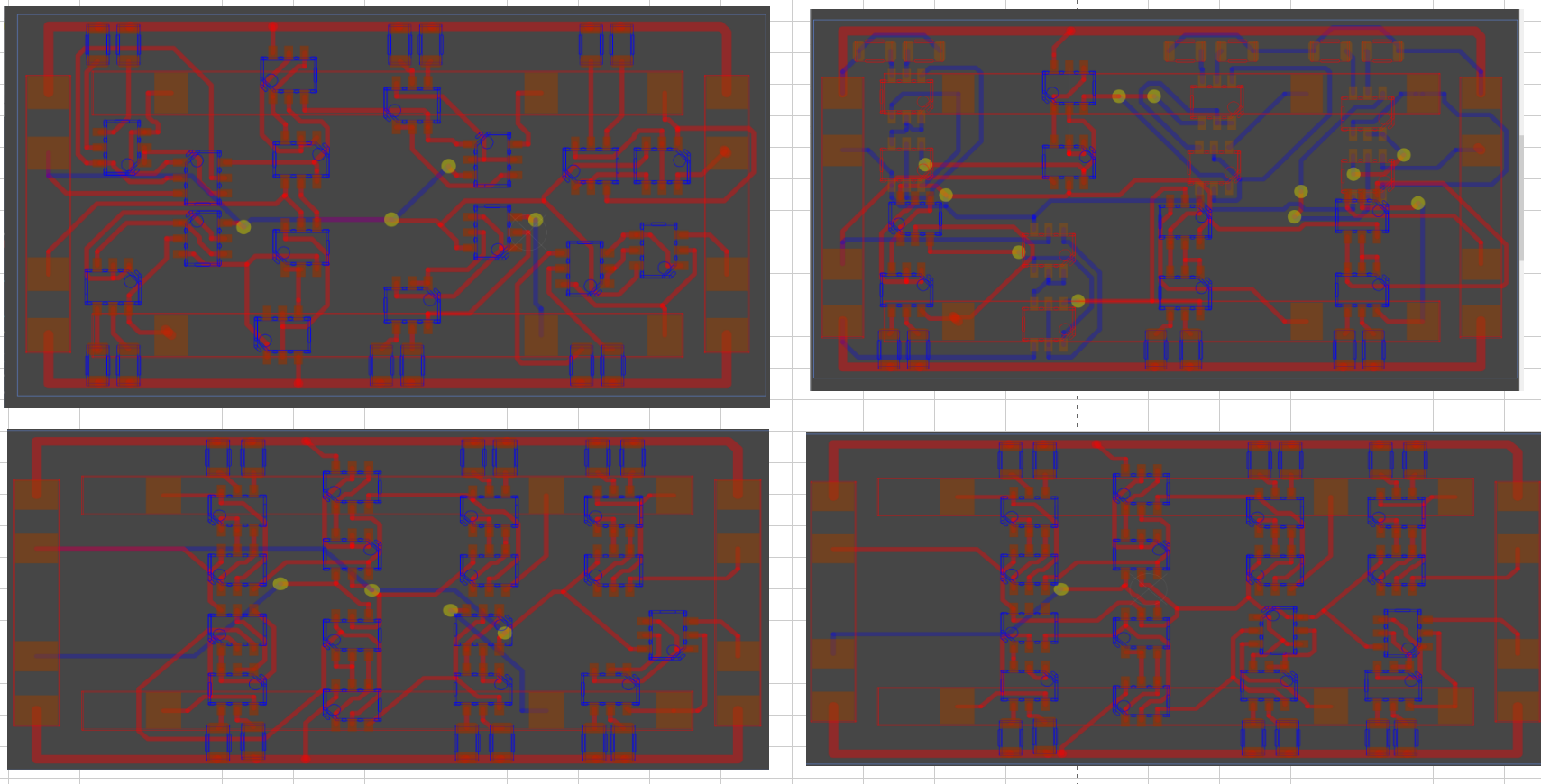

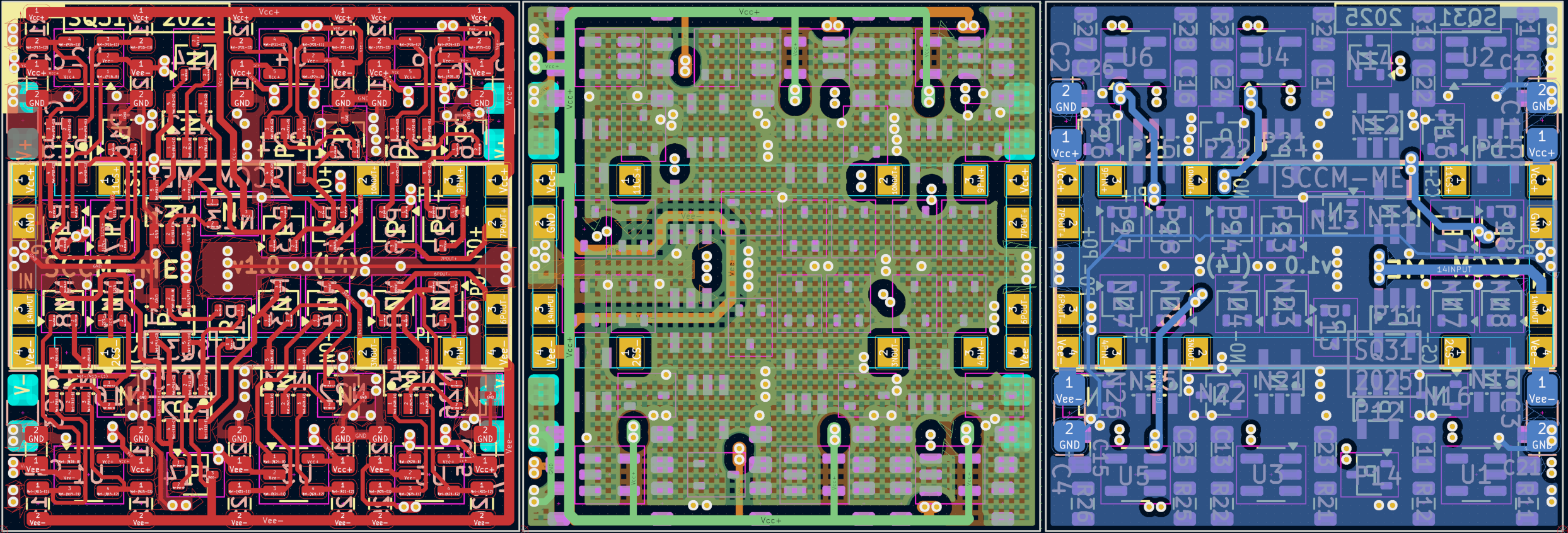

基板デザイン

プリント基板デザインについては、入力バッファ「HBD」設計時に確立した

「適当に部品を置いて自動配線で試行回数を稼いで、

よさそうな案をさらに煮詰めて(配置微調整&自動再配線)、出来上がった最終案を手配線で清書する」案にて進めました。

自動配線活用にて表裏2層でも配線はできてしまったのですが、今回は人生初の4層基板の製造発注についても検証してみたいと思っていました。

とはいえ内2層は単なるGNDベタとしてしか使っておらず勿体ない仕上がりとなっています。

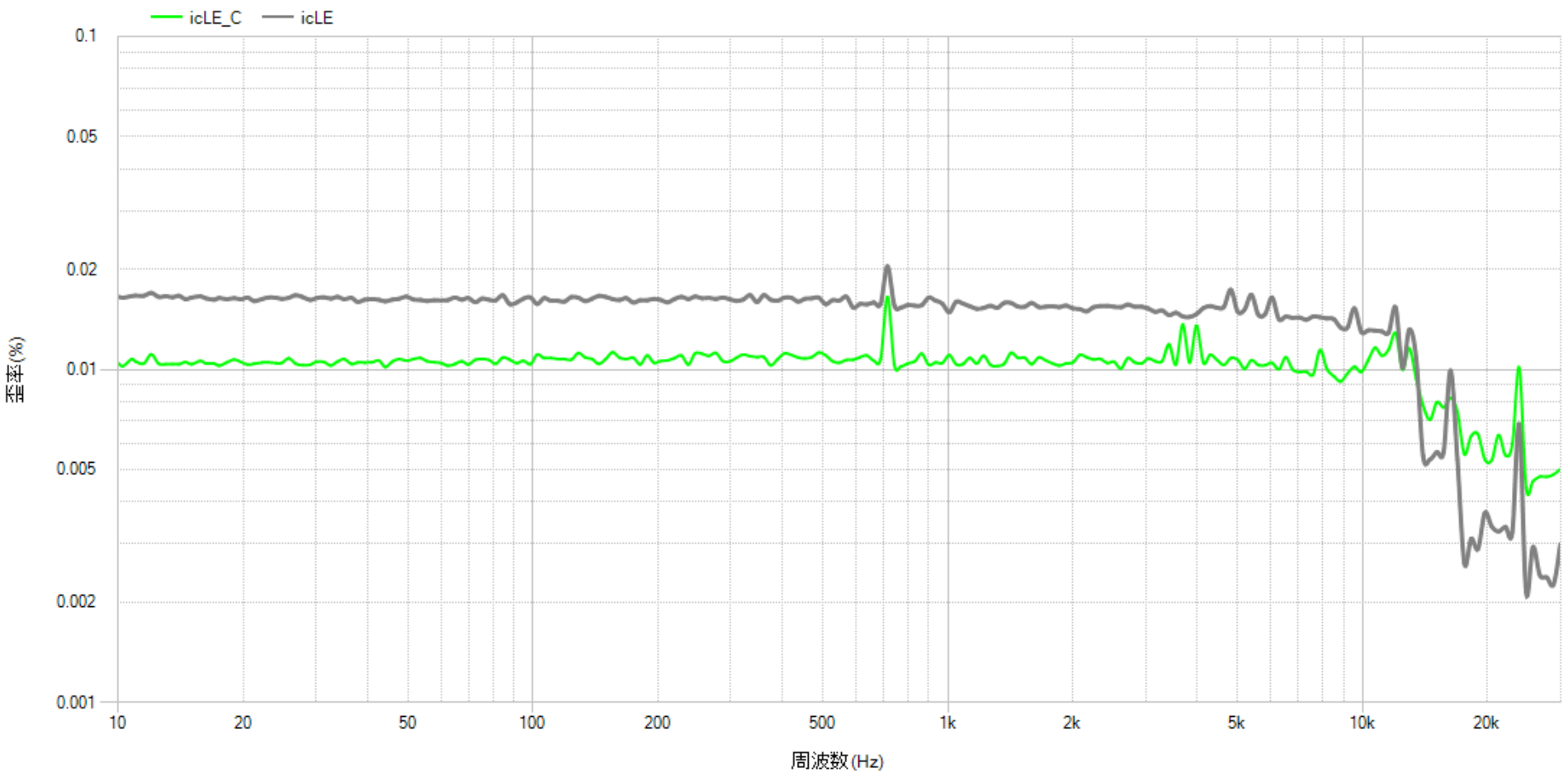

ハイブリッドICのフットプリントですが、足は2.54mmピッチになっていて扱いやすいです。

なお、1:Vcc- と 5:Vcc-、および 8:Vcc+ と 12:Vcc+ は基板内で接続させておく必要があります。

これはV4.1デザインがそのようになっており以後踏襲されており、

また5・8ピンを電源入力として使い1・12ピンを入力バッファ向け電源出力として使っている製品例があるためです。

製造留意点

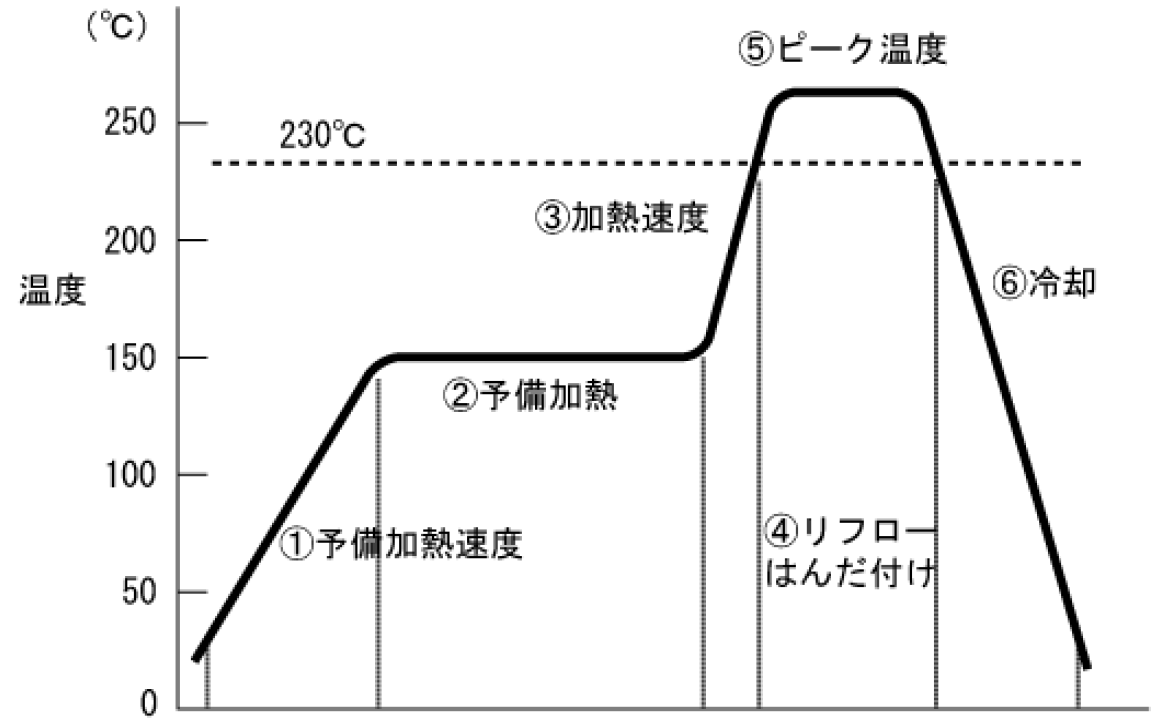

リフローはんだ作業手順についてはネットの記事、Youtubeの電子工作系の動画などを参考にしました。

中国製の激安な研究用ホットプレートを使い自宅リフローしている事例も多いです。

1万円以下で100W~400W級で300℃超になるリフロー用機材がゴロゴロしています。

個人的には様々事例調査して機器選定して、各種道具も合わせて調達しました。

- ホットプレートは 10cm x 10cm 出来るモデル(プリント基板を安価製造できる10cm x 10cmサイズ対応)

- クリームはんだ(ソルダペースト)は183℃通常品

- 金属ブラシ、プラスチックのヘラ、洗浄用アルコール(無水エタノール)、フラックス(粘度調整)など道具・薬剤も用意

リフローの製造詳細は省略しますが、何度かやってみて失敗成功繰り返さないと体得できず難しいと感じました。

クリームハンダ塗るのもコツがいるし、ハンダ多過ぎは大失敗するけどごく少量でも上手く部品が付かなかったり、

温度も予熱と加熱のタイミングが相当むずかしいです。

もちろん適当でもそれなりに出来るのかもしれませんが、正しく行うと加工成功率が向上すると分かります。

プリント基板と同時発注したステンシルを利用しましたが、クリームはんだを塗る量、

リフローの事前余熱や加熱のタイミング、部品セリフアライメントには頼れない点などなど、

失敗しなければ身につかないですがとてもいい経験でした。

できるだけ成功率を上げるように工夫は積み重ねています。

(1)クリームハンダは多く塗り過ぎない、何度もヘラで往復しない(かといって薄すぎもダメ)

(2)仮に基板2枚作りたいとするとリフロー作業は3枚するようにして、その前のクリームハンダは4~5枚塗って出来がいいものを選別して使う

部品メーカーなどのデータシートにはリフロー温度条件が記載されています。

これらも参考にしつつ解説動画も複数参考にして予備加熱は必要十分に行い、ピーク温度(設定温度)も220℃~230℃で行うこととしました。

あとは数回行うとコツがつかめてきました。

リフロー後、ハイブリッドICなのでピンを取り付ける必要があります。バッファHBC/HBD同様に細いピンヘッダでも問題なかったのですが、 マックエイト社(MAC8)のハイブリッドIC用のピンヘッダとすることとしました。 リン青銅や黄銅で出来ており、SATRI-IC同様の細くて強度があるピンで抜き差ししやすくなります。

最後、フラックスクリーナーで作ったプリント基板を洗浄しておきます。 コスパ・使い勝手からサンハヤト製 FL-500 を推奨します。

計測・テスト

電源投入前にルーペ等を使ってハンダ付けを確認します。

工場での機械生産ではないのですからハンダミスがあると疑った方がよいです。

ハンダブリッジなどはこの段階で不良摘出して対処を済ませておきます。

引き続き通電前に、たとえば電源ピンや入出力ピンとトランジスタの足の抵抗値をテスターで計測します。導通が無ければハンダ付け不良を疑います。

全部が計測できるわけでは無いのですが可能な範囲だけでも実施すると不良を事前対処することができます。

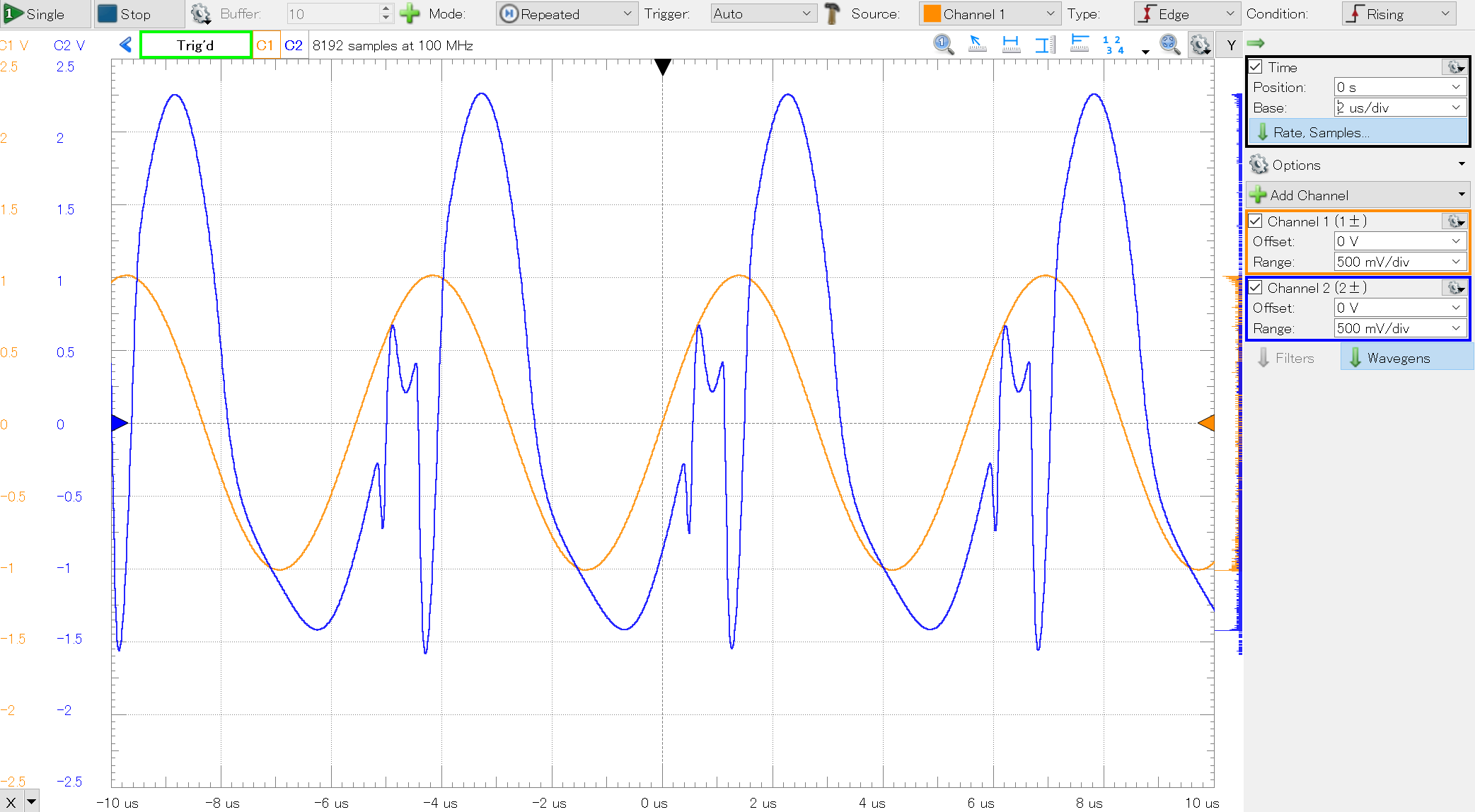

次に電源接続したうえでハイブリッドIC単体で動作確認します。個人的にはプリアンプ基板(PRIAMP-W 基板)をテスト用途に使っています。

最初は入力0V(入力とGNDをショート)として短時間だけ電源オンして、出力にオフセット電圧が出ないことをオシロスコープで確認します。

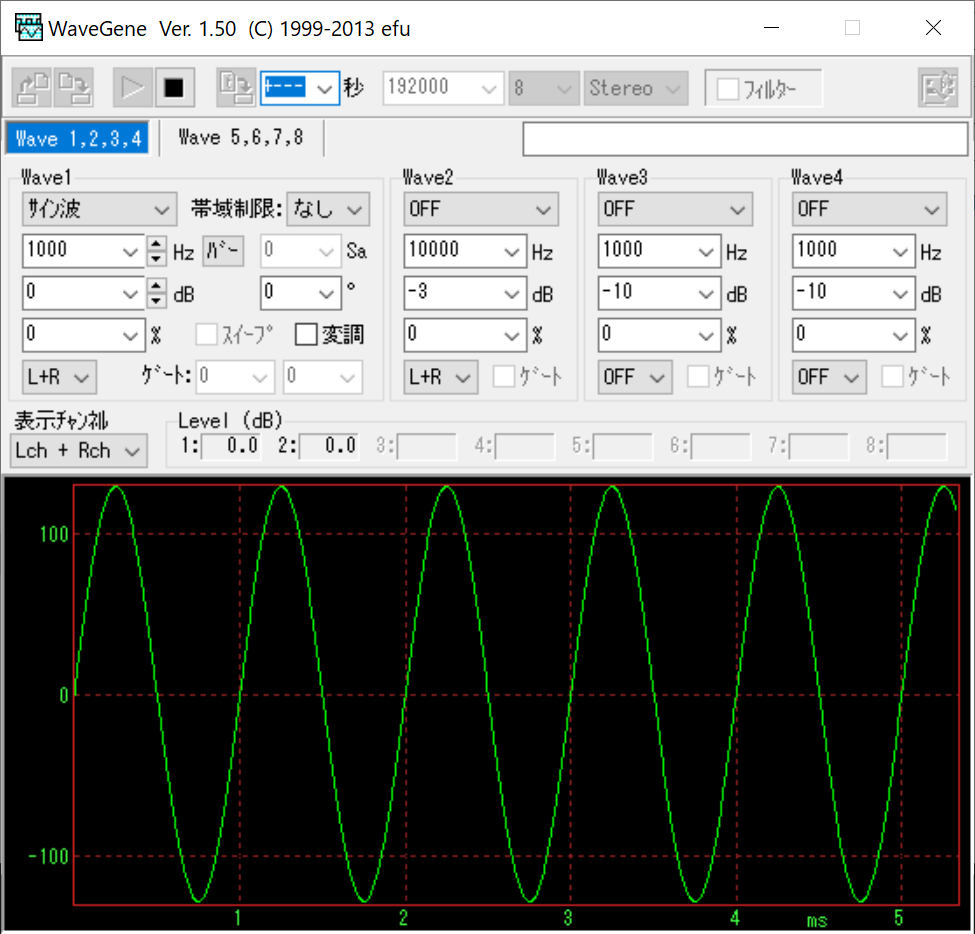

問題無ければ、サイン波 (1kHz~40kHz位(可能なら80kHz位まで)) を流してオシロスコープで確認します。

テスト入力信号のサイン波の発生にはPC用の信号発生ソフトを使っています。efuさん作の WaveGene というソフトです。

2024年9月からweb archiveではなく本家からダウンロード可能となっています。

https://efu.sub.jp/soft/wg/wg.html

PCサウンド機能を使うことになるのですが、

きっちりテスト信号出すなら廉価品でいいのでDTM入門機とかのオーディオインターフェイスが良さそうです。

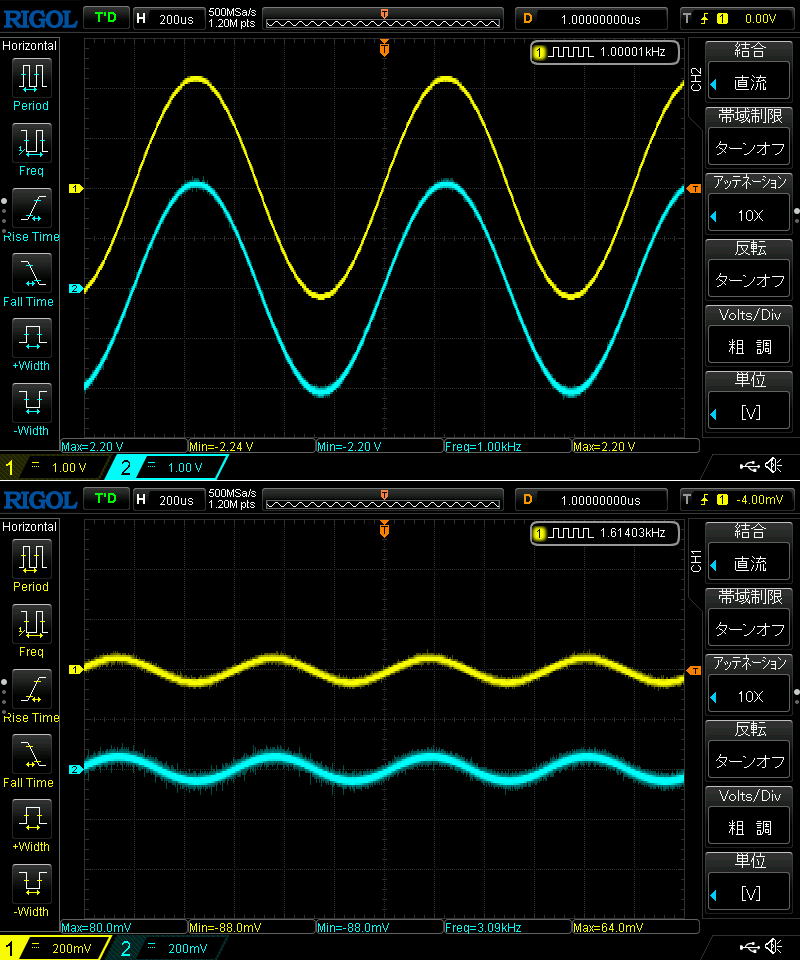

実際の波形の例です。波形:左は正常です。なお小さい電圧・小信号(波形:左下)を流すと発振が見つかることがあったので個人的には毎回確認しています。

波形:右はハンダ付け不良により問題があった例です。波形:右下のように明らかにおかしい波形なら気付くと思いますが、

波形:右上のように少しだけ問題があるとオシロスコープで詳細確認していないと見つけることが困難です。

原因はハンダ付け不良であり、トランジスタの足がパターンに正しくハンダ付けが出来ていないというものでした。

設計補足、部品留意点

- 表面実装トランジスタ(dual BJT)はマッチング補償品を採用しています。ピン配置は当該メーカー専用となっています。 複数の半導体メーカーにある汎用品BJTのピン配置とするにはプリント基板の新規設計が必要となります。

- 抵抗については表面実装チップ抵抗となりますが、コストパフォーマンスと音質から薄膜チップ抵抗を推奨しておきます。

逆に厚膜チップ(メタルグレーズ厚膜抵抗)は音質面から個人的には非推奨です。

ネット自作記事を探すと音質比較評価などもありますので、まずはコスパよい品で試してみることを強く推奨します。

またカレントミラーの精度向上のため高精度品( 抵抗温度係数[ppm/℃] が小さいもの、 抵抗値許容差[%] が小さいもの) を推奨します。今回利用したチップ抵抗は、温度係数:25ppm/℃、公差:0.1% のものです。

感想・反省点・今後の課題

SCCM-LE の音は、手持ちの既存 SATRI-IC(対象:V4.3、SP、UL)とはどれとも違う傾向の出音でした。

とてもとてもスッキリしていて中高域張りだした元気な音が出てきました。

クリアで解像度が高い音ですが、音が滲まずどちらかといえば軽めな音という感じもあります。

コレが最良というわけではないとは思いますが、この尖り具合と切れ味はとても面白いと思いました。

このサブプロジェクトの目的である「リフローはんだ製造技術の習得」についても行うことが出来ました。 とはいえ一発動作するほどの製造技術の確立は困難でしたが、通電前にルーペ検査して はんだごて で概ね修正出来ており、 計測テスト作業をすることにより100%動作するものが作れています。

改良

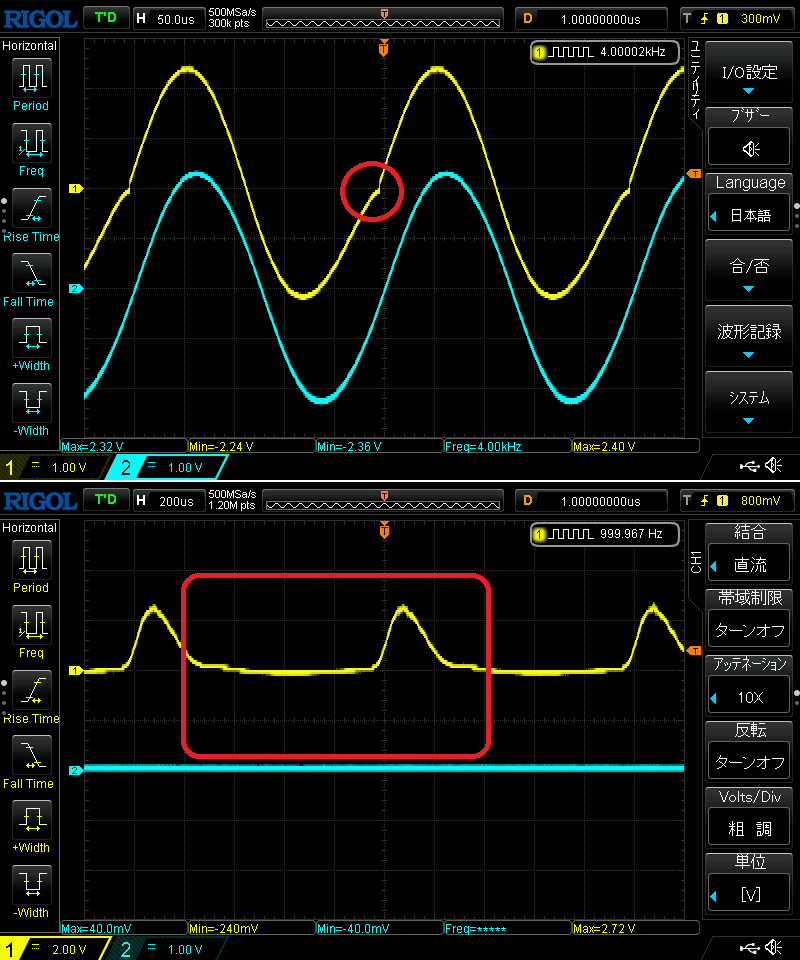

後述 SCCM-UT v1にてモジュール上へのパスコン搭載の効果があったのでSCCM-LEでも実施してみました。

レジスト削って MLCC 1608M サイズの 330pF x4個 を取り付けましたが、

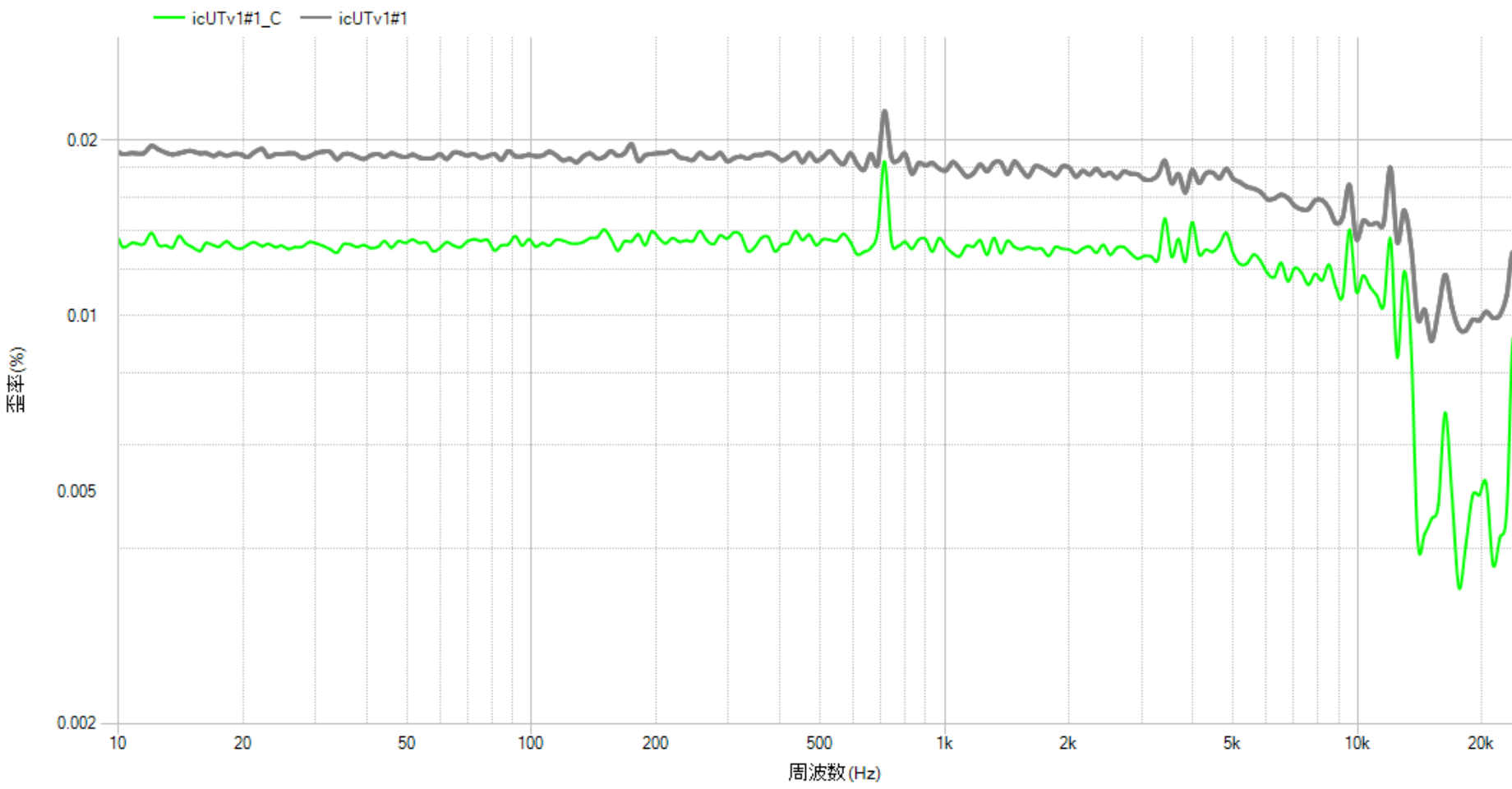

当初(グラフ灰色)から変更後(グラフ緑色)のように改善しました。少なからず効果があるようですね。

とはいえ課題もあり、適切な容量が分からない点(100pF ~ 1000pF あたり)、

MLCCだと少容量だとしても若干は音に色が付く点ですかね。

コンデンサはメーカー・品種など選ぶでしょうし、効果には計測や比較試聴も必要だし、難しいとは思います。

あとツールを使った歪率ですが低ければ音がイイというものでもありません。既に聴覚限界ですし。

とはいえ同一モジュールで手を入れる前後で改善しているのであれば効果があったと評価はできます。

コンポーネント:SCCM-UT v1 (電流入力 Hybrid-IC 音質向上版)

概要

『 SCCM-UT 』は SATRI-ICピン配置 の ハイブリッドICモジュール です。

作業時期は設計着手 2024年3月、音出し 2024年5月 です。

前述 SCCM-LE を超える音のハイブリッドICを作るべく、SATRI-IC-UL ピン配置・機能互換として設計したものです。

(個人的には詳しくないのですが)東芝 の 低雑音トランジスタ では

自作アンプ界隈では昔から定番のスルーホール品 2sc2240 ・ 2sa970 というのがあったとのことですが既に生産終了のようです。

その同系統と思われる表面実装トランジスタについては現行品のものがあります。

一応、海外メーカーのトランジスタでも低雑音品はありますが、比較すると更に低雑音である東芝製BJTのみでICモジュールを作ってみることにしました。

設計

基板サイズについては SATRI-IC 標準サイズ 30.5mm x 14mm は早々に断念して30.5mm x 32mm を最大サイズとして、

(プリアンプ基板などの)被搭載基板は空間余裕をもってデザインすることとしました。

回路図。Dual BJTが実装しやすい形をしているとはいえ、お化けのカレントミラーです。

写真

SCCM-UT の写真です。

写真:左、BJT 72個、更にデュアルトランジスタ SOT23-5 は( SOT363-6 より)一回り大きい事もあり、基板サイズは相当大きくなりました。

写真:右、SCCM-UT と SATRI-IC-UL とを比べると2倍のサイズがあります!。

モジュールICの表面のみ半導体実装としたのは自宅リフロー都合です。

感想・反省点・今後の課題

試作したハイブリッドICの SCCM-UT ですが、 音は SCCM-LE と比較して異様さを感じるほど格の違いを見せつけてくれました。出音はかなりよかったです。 (SCCM-LEのとにかくクリアで軽い出音と比較すると)SCCM-UT は情報量がある音に加えて、 音に濃さと色気があってオーディオ的な気持ち良さがある出音でした。

しかし本サブプロジェクトの主目的であった「リフロー製造検証」としては製造問題が複数ありました。 その要因としてはプリント基板デザインに考慮不足があり、 デュアルBJT素子は(SCCM-LEと比べ)比較的大きくてハンダ付けしやすいにも関わらず、 リフロー後の手直しも多数発生しました。 その手直しのハンダ作業も、ビアにて中間GND層に吸熱されてしまい異様に苦戦しました。 リフローそのものではなく、プリント基板デザインに反省すべきことが多々ありました。

コンポーネント:SCCM-UT v2 (電流入力 Hybrid-IC 音質向上・パタン見直し版)

概要

プリント基板を再デザインした SCCM-UT v2 を作成しました。

回路およびトランジスタ・抵抗等の部品については全く同一のものになりますが、縦方向は30mm → 31.2mm に若干サイズ広げて余裕を持たせました。

前回のリフローはんだ作業で問題あった個所についてはプリント基板のパタンの大幅見直しを行い、

またリフロー作業も5基板目ということでクリームはんだを塗るコツも多少身につけており、

その上で複数枚塗って塗布状態で選別するなど失敗率低減も行っており、それらの積み上げでにて上手く出来たと思っています。

設計

プリント基板のデザインについては表裏2層で配線は済ませていますが、そこに中間2層GNDを足して計4層でデザインしています。

ノイズ対処面で効果がうまく出てるとイイのですが、素人の私では評価が難しく。

なお入力バッファモジュールで効果があった表面実装コンデンサを追加できるように裏面にパタンを追加しています。

製造・計測

新規導入したデジタル顕微鏡(4K)も活用することでチェックやハンダ訂正作業などなど作業効率をアップさせています。

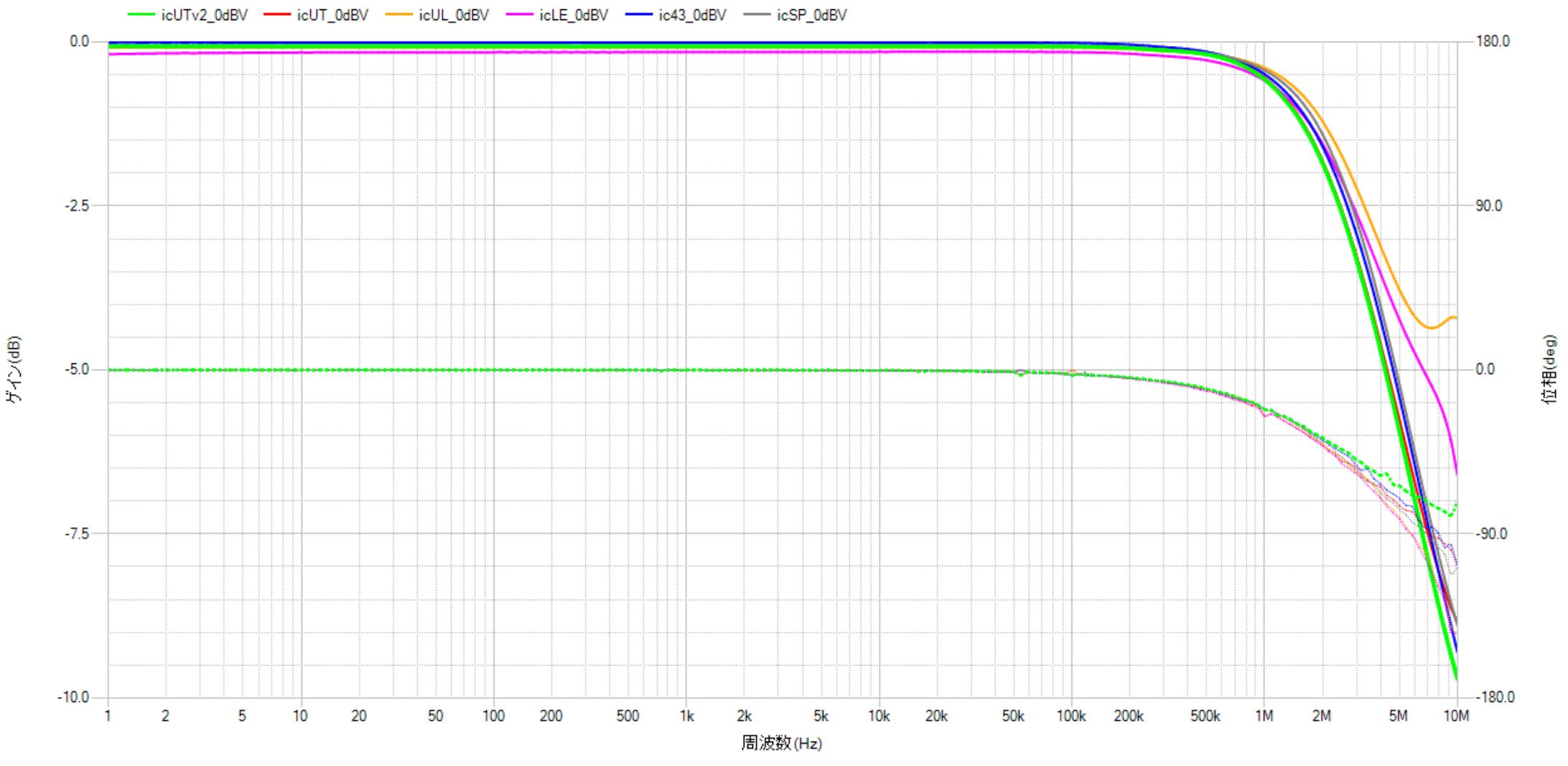

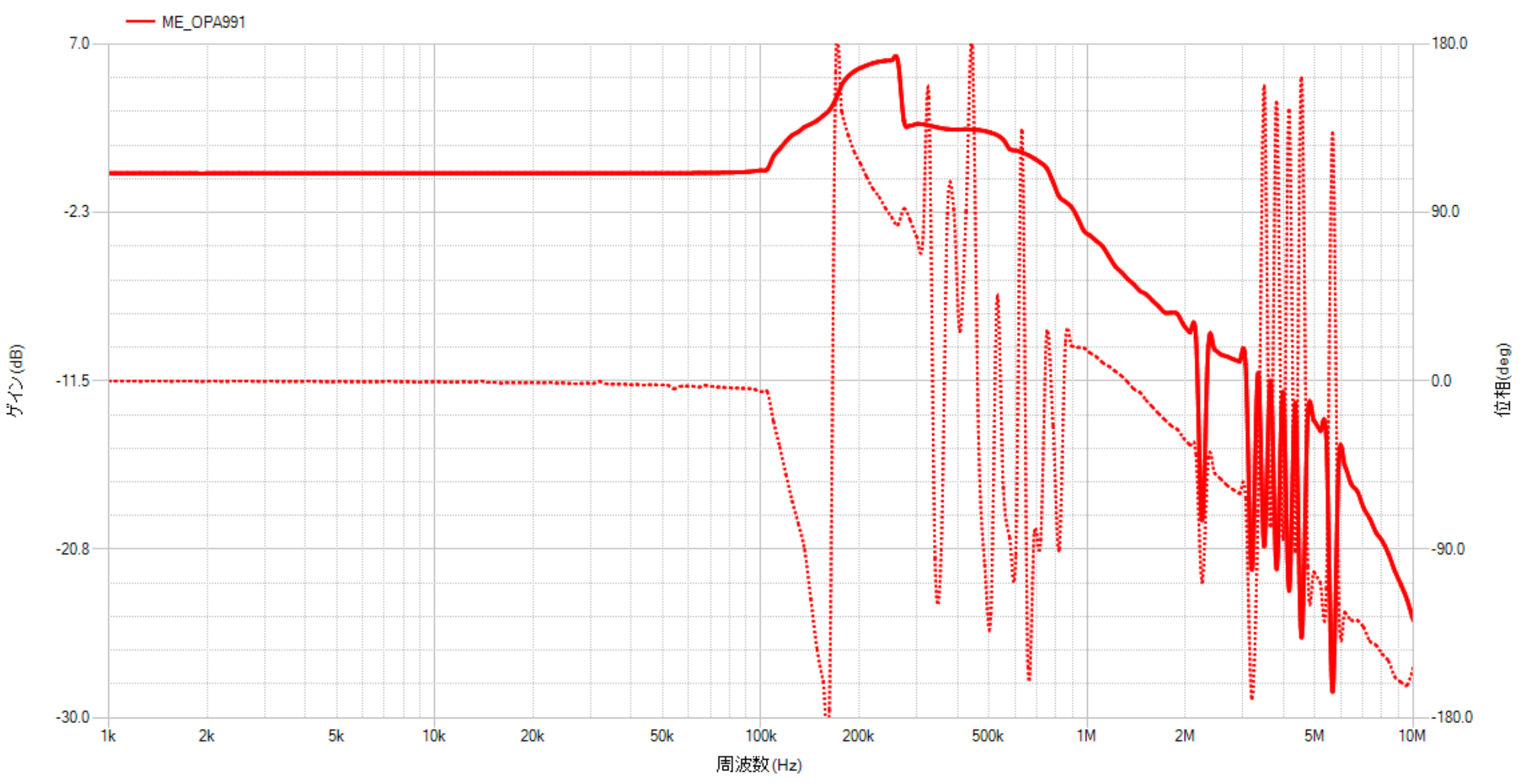

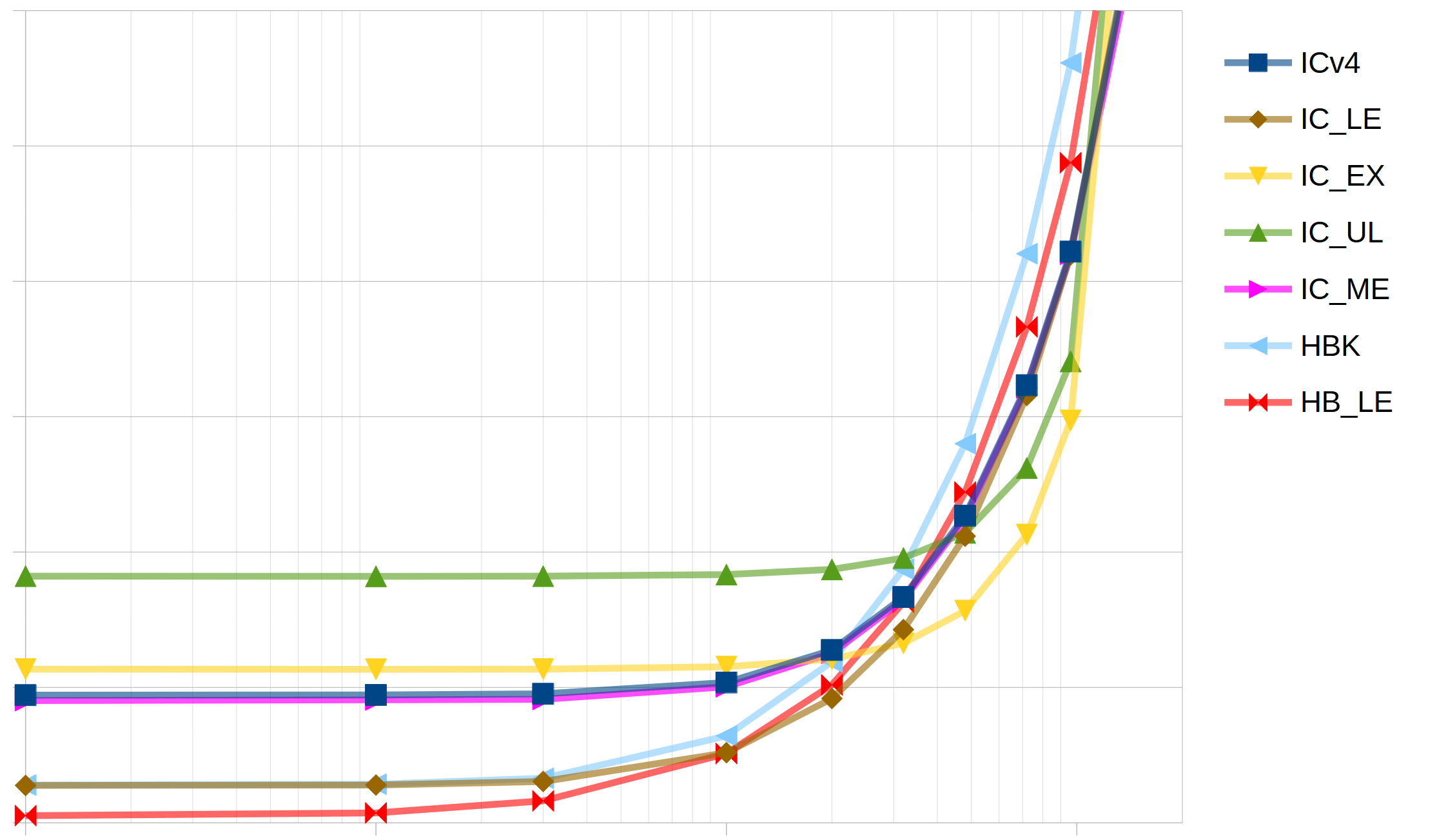

(左図)計測ツールを使って周波数特性を計測(Analog Discovery2 + 自作テスト基板 + ソフトFRAplus)。

特性差異はあまり見受けられません。

(右図)グラフを拡大すると差異は分かりやすくなります。

初期のSATRI-IC v4.3(グラフ青色)が入出力差異が少なく、

自作のSCCM-LE(グラフ紫色)が大きいですが、これはそこまで音質影響は無いと感じています。

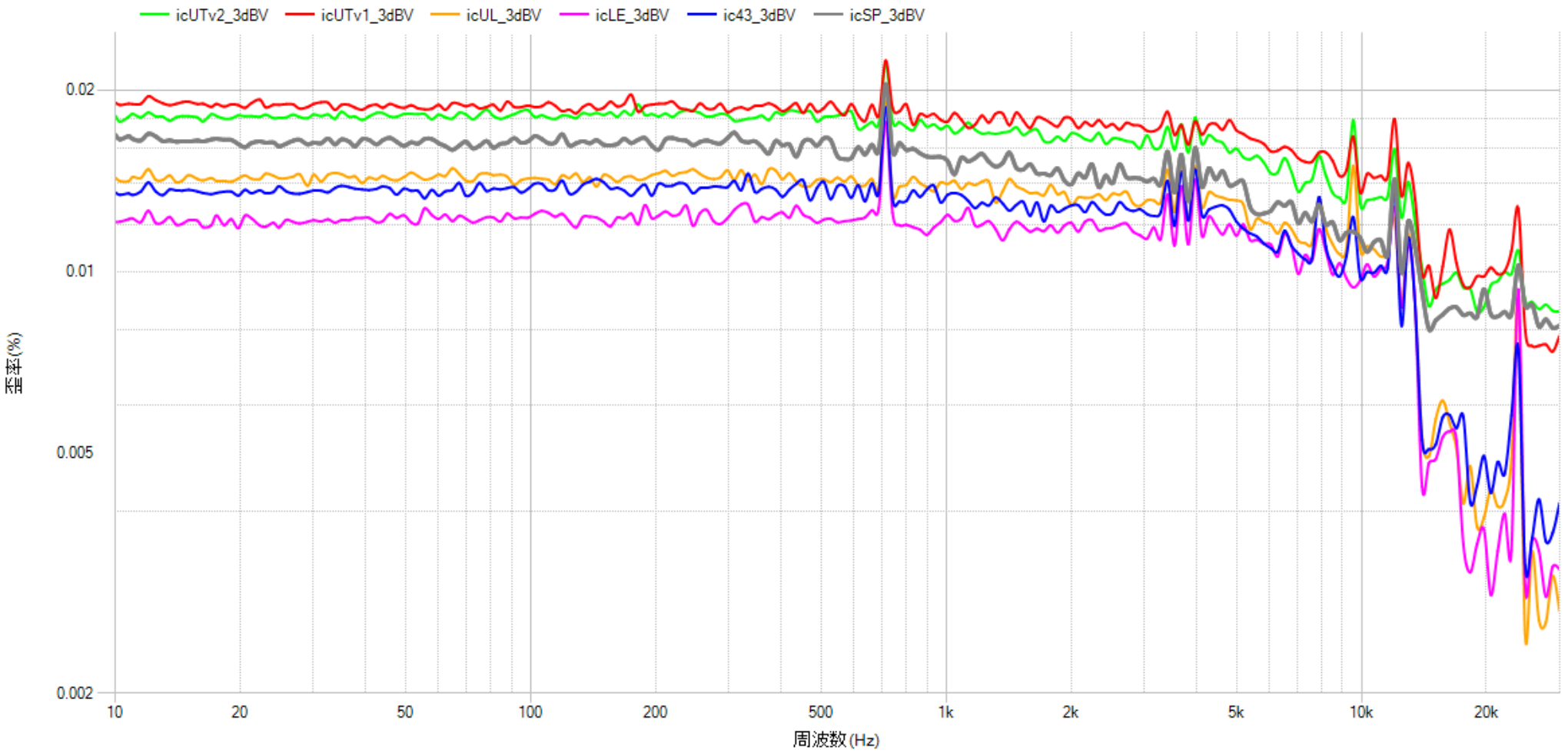

同計測ツールで歪率を見ると、旧基板SCCM-UT v1(グラフ赤色)と、

今回の新基板SCCM-UT v2(グラフ緑色)ですがほぼ一緒です。

この2つは載ってるトランジスタ等の表面実装部品は同一なので、若干の差異はパタン設計、あるいは自宅リフロー作業の慣れ不慣れ、

そういうのが影響しているのかもしれません。

なおツール「 Analog Discovery2 + FRAplus」は非常に使いやすいですが、

レンジが切り替わって計測結果が歪になることもあるので評価には注意する必要がありそうです。

SCCM-UT v1 から SCCM-UT v2 の変更点では、

オプションで表面実装パスコン 3216M (2012M) を(モジュール基板裏面空きスペース)電源ラインに載せられるようにしていまして、

実際に 0.015uF 程度の音質定評あるフィルムコンを載せていました。

他のモジュール設計作業(バッファ)では聴感上の変化があったためです。

古い設計の SCCM-UT v1 には 3216M~2012M を載せるようなスペースがありません。

改良してみるとしても、手持ち積層セラミックコンデンサの極小 MLCC 1005M 1000pF (C0G)は 一般人には実装厳しいレベルだったので、

次点の MLCC 1608M 680pF を電源ラインのレジスト削って実装してみました。

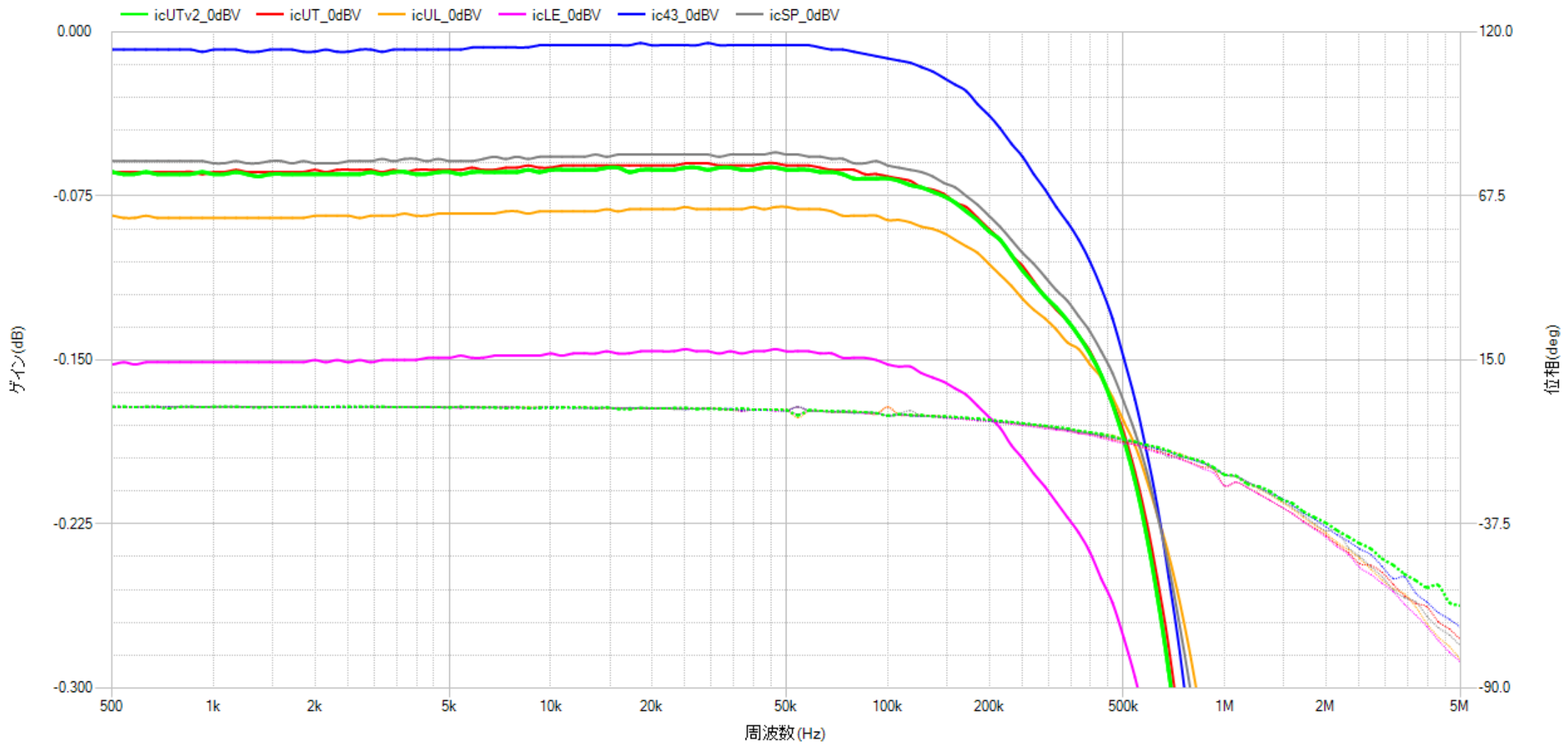

計測ツールで歪率を見ると、基板SCCM-UT v1 パスコンなし(グラフ灰色)と、

基板SCCM-UT v1 パスコンあり(グラフ緑色)比べると結構改善しています。

0.015uF から 680pF だと静電容量 1/20 (※100MHz超のパスコン)ですがそんなところが出音の改善につながるとは予想もしませんでした。

昔からSATRI-ICを使う場合、低ESR固体電解コンデンサ (OS-CONなどの導電性高分子アルミ電解コンデンサ)を

モジュール直近に4個設置というのがお約束でして長年疑っていませんでした。

今回、小容量MLCCをカレントミラーの直近に配置したわけですが効果が少なからずあるようです。

とはいえ課題もあり、適切な容量が分からない点(100pF ~ 1000pF あたり?)、

MLCCだと少容量だとしても若干は音に色が付く点。後者はメーカー・品種などもあり悩ましい所です。

実際の出音も低域のアタック感が強くなった気がします。

更に他のモジュールでも同様のパスコンを試しましたが効果が無いケースもありました。

基板デザインや使っている半導体でも変わってくるかもしれません。ここで0.1uF~0.01uFなら音の色付けという使い方は出来そうですが、

pF 小容量パスコンは評価しないと適切な値は難しいかもしれません。

コンポーネント:SCCM-ME v1 (電流入力 Hybrid-IC 別方式版)

概要

SATRI-IC ULを超えるには?

長年検討していましたが、世界中のカレントミラーの学術論文を読み漁っているときに別方式を思いつきました。

トランジスタ1個と差動増幅回路でもカレントミラーが構成できますが、そこを多段&ベース電流補償型にしています。

集積回路を更に集積したハイブリットモジュール、音響的にはサッパリ予想がつきませんが試してみる価値はあるかと思い作ることにしました。

設計

回路図です。反則技とはいえ集積数が凄まじい事になっています。

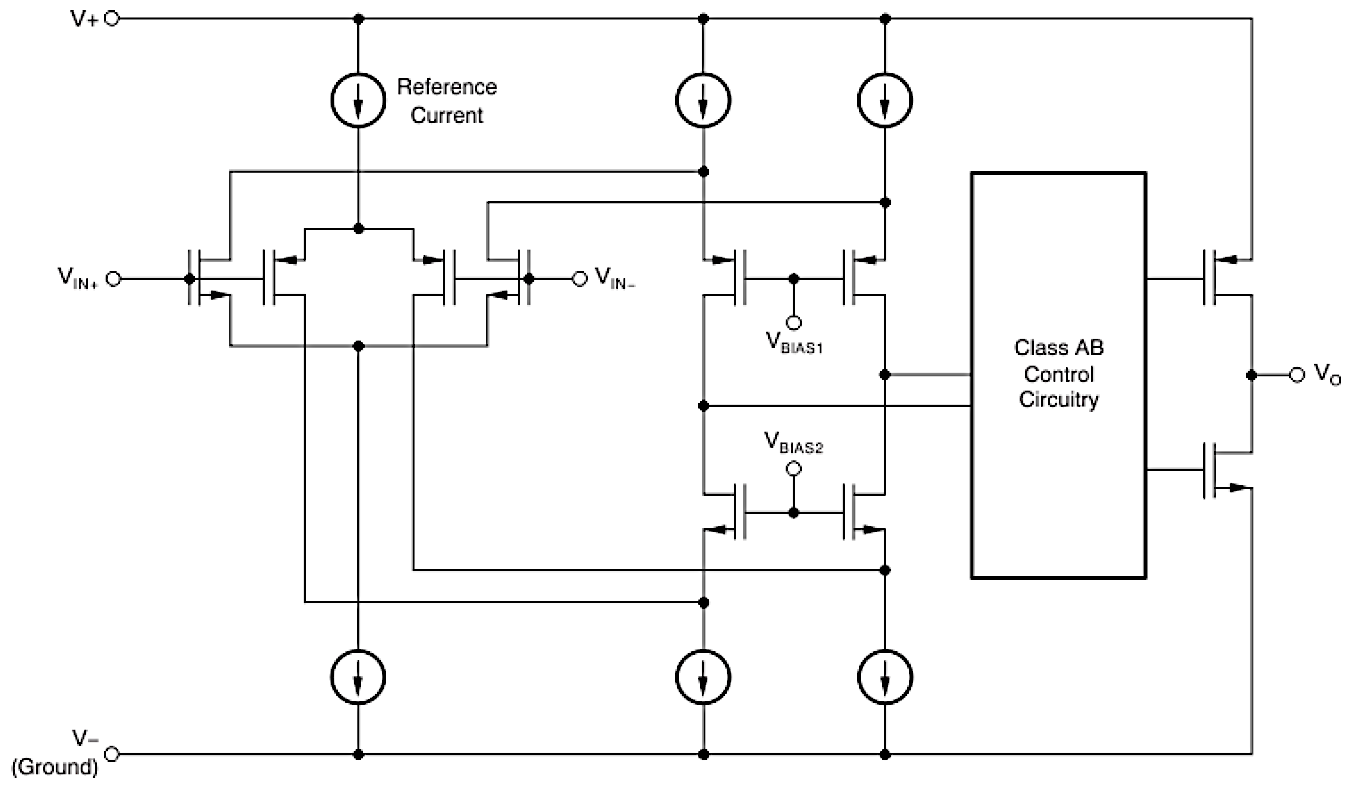

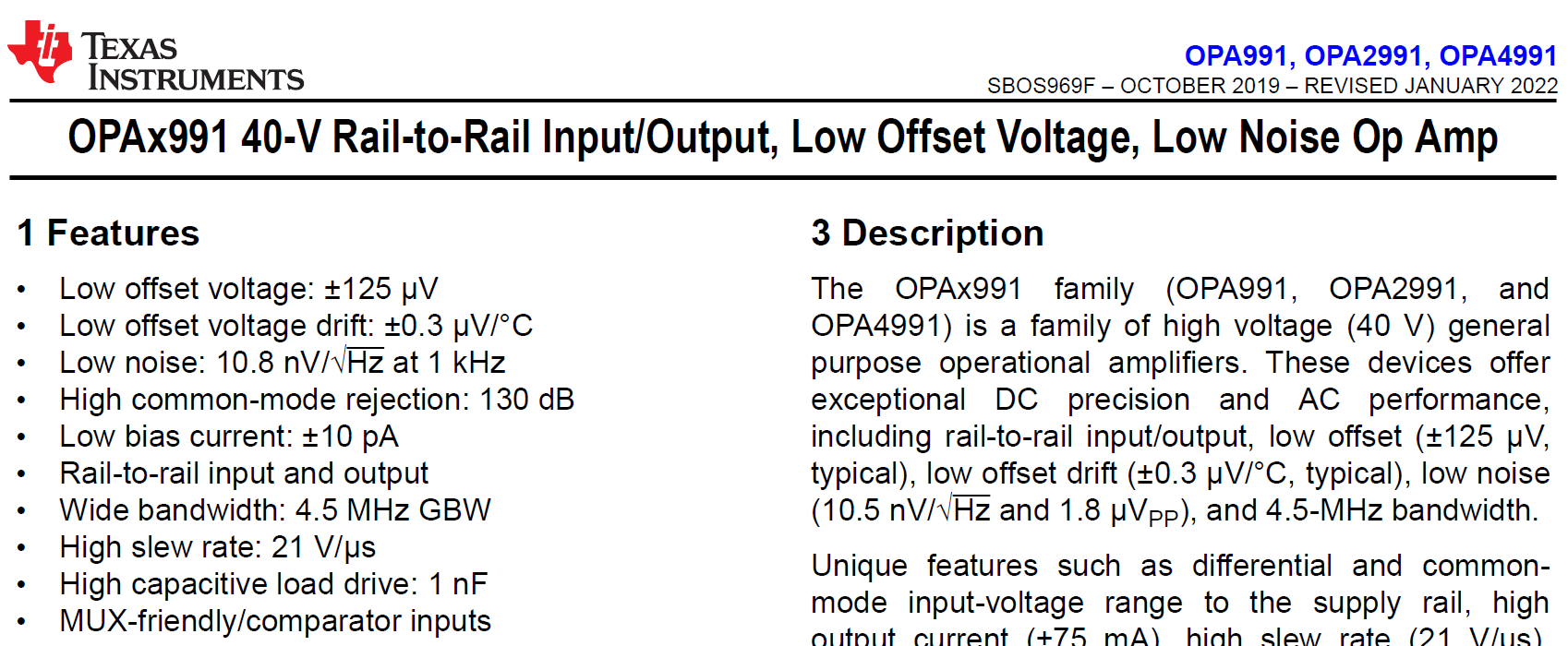

ただし正負オペアンプともに電源近傍でスイングすることになるため、

入出力レールツーレール(rail-to-rail input and output、フルスイング)タイプのオペアンプが必須となります。

具体的には入力にNchとPchのFET差動対が並列にあるタイプです。

これらは製品によって違いますが、電源電圧±0.1V~±0.2Vでも動作するものがあります。

プリント基板のデザインについては表裏2層でも辛うじて可能でしたが、中間2層を足して計4層でデザインしています。

代わりにオペアンプとカレントミラーの電源ラインを分けて更にGNDも配慮してノイズ対策面では多少工夫が出来たと思いますが、素人の私では評価が難しく。

製造・計測

リフロー製造して、計測ツール(Analog Discovery2 + 自作テスト基板 + ソフトFRAplus)で評価してみます。

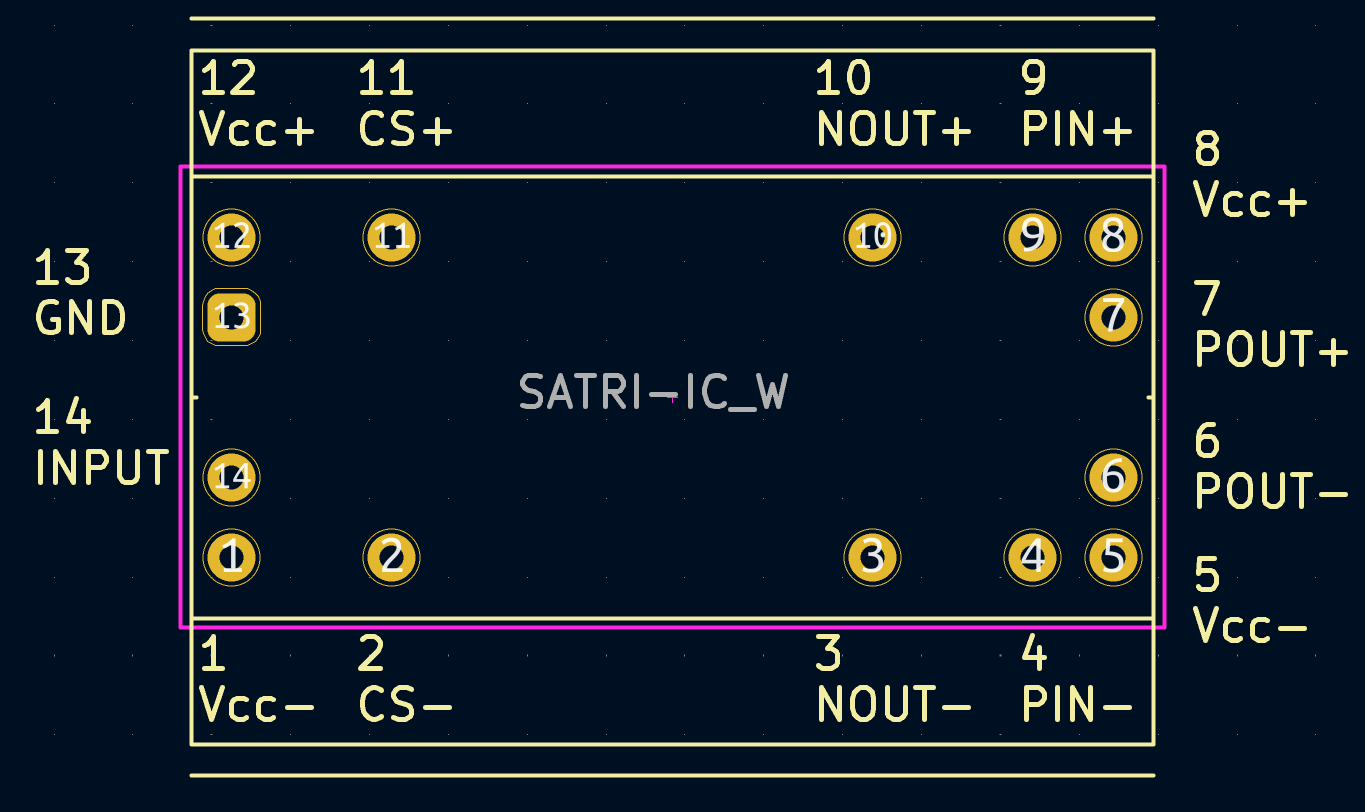

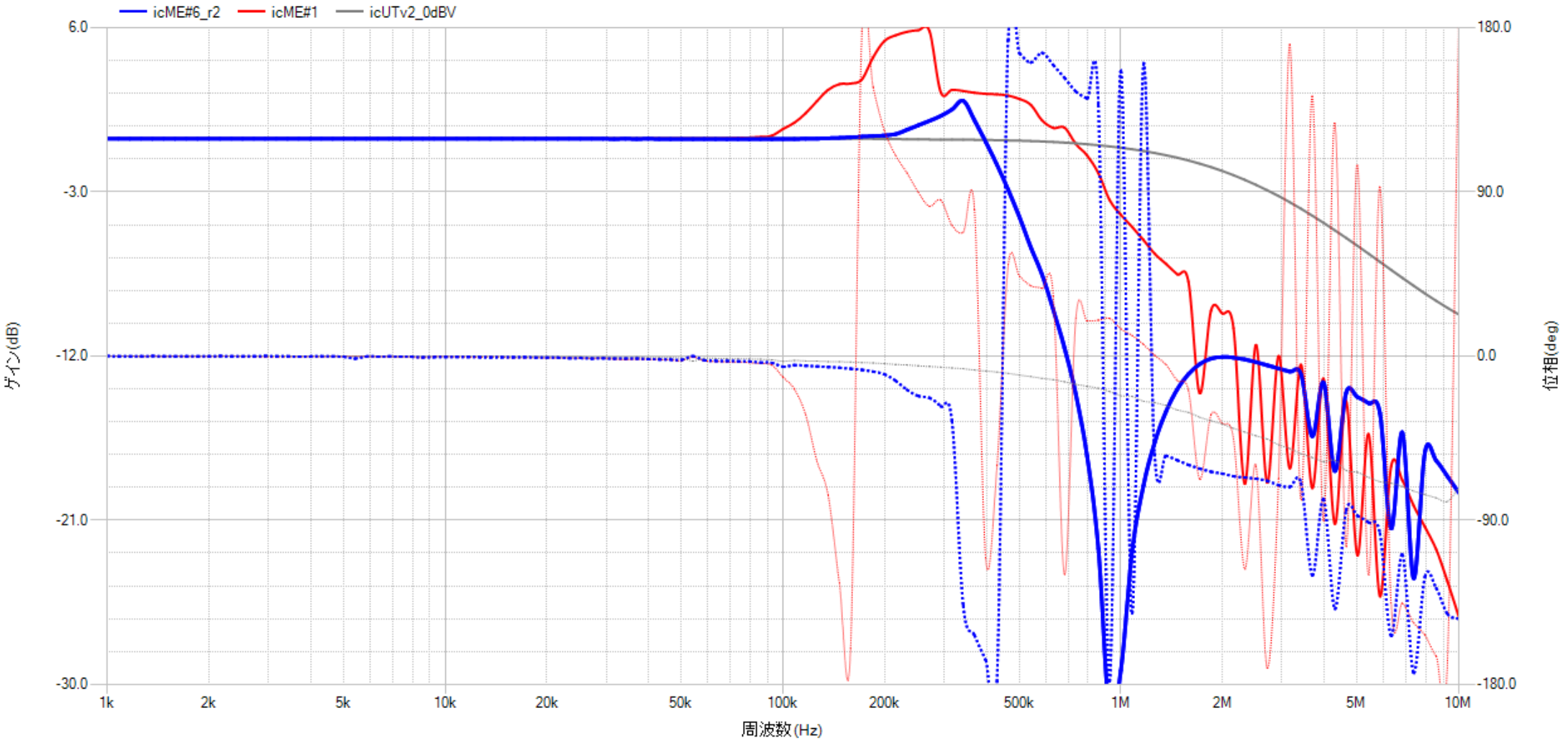

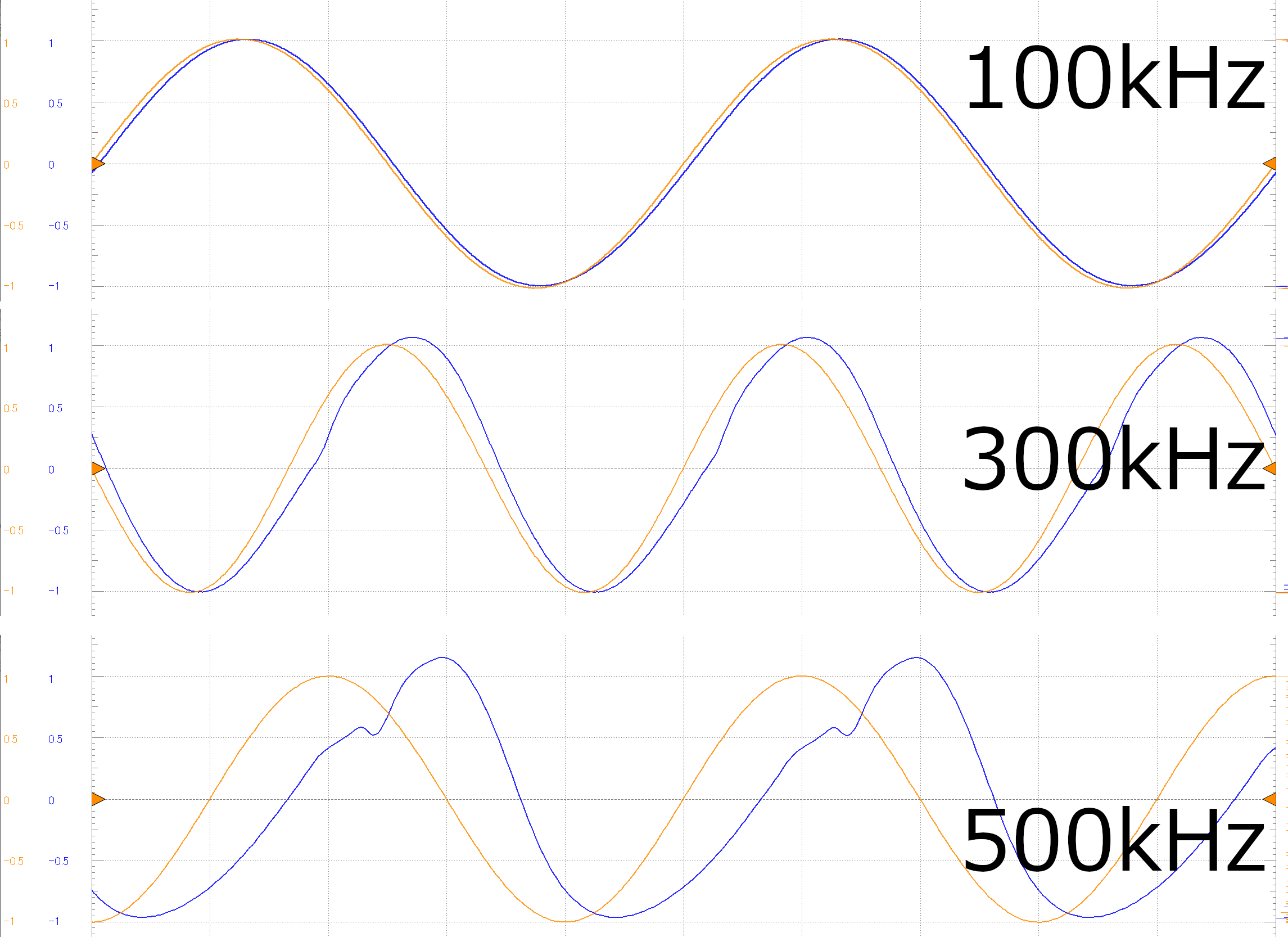

(左図)周波数特性見ると150kHz以上で大きく歪んでいます。

(右図)波形をツール(Analog Discovery2 + 付属WaveForms)で見ると

入力(グラフ橙色)と出力(グラフ青色)の状況が分かります。

ここでプリアンプ基板には複数の発振防止策が組み込まれており、実際に搭載してみると実用上は問題ありませんでした(グラフ緑色)

実際に聞いてみるとかなり攻めた音?!でした。

RRIOオペアンプを使うとカレントミラーの電流コピー精度がより高くなるというのと、超高域での歪み、MLCCパスコン使用など幾つかの要因があり、

それらに起因しているのかもしれません。

とはいえ計測ツールで更に確認するとSCCM-MEの歪み率(左図、グラフ紫色)が飛びぬけて悪く残念な結果となっていました。

当初、LTspiceシミュレーションで歪み率比べてみた時でのSCCM-ME(右図、グラフ紫色)はイケると思ったのですが、

現実の回路(左図、グラフ紫色)ではそうはならなかったようです。

その後も諦めずに色々弄って検証続けていました。

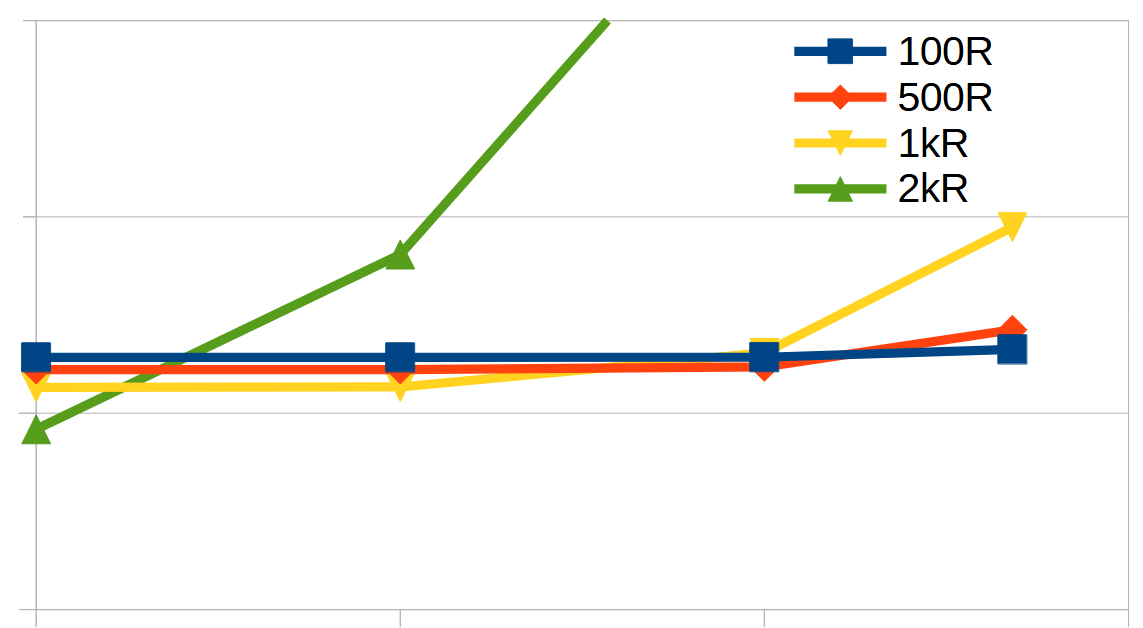

初期のモジュール設計時点に残した資料を読み返すと、

LTspiceシミュレーションではカレントミラーのエミッタ抵抗を1kΩ以上にすると歪み率など悪化したことを書き留めていました(右グラフ)。

(RRIO動作とはいえ電源電圧ではスイング出来ないため高めにしていたエミッタ抵抗について)

逆にエミッタ抵抗値を下げてみると200kHz超まで抑制することができ、

SCCM-MEについて 当初(グラフ赤色)から変更後(グラフ青色)のように改善しました。

200kHz超であればプリアンプ回路に当初から発振対策を複数設けてあるので辛うじて使えそうです。

ただしエミッタ抵抗を小さくすると入力信号がより電源電圧に近くなり、更なるRail-to-Rail-Input性能を要求されるようになります。

今回予備含めて複数種類のRRIOオペアンプを用意していましたが使えないOPAMPも出てきました。

変更後も10kHz以上は歪み率は悪化する傾向が残っています。

当初(左グラフ赤色)と変更後(左グラフ青色)ですが、

周波数が高くなるにつれて位相が遅れて歪んできています。

(右図)実際の波形を見ると、これが実際の聴感上でどれだけ影響があるのかは未知数です。

感想・反省点

初代ハイブリッドICモジュール SATRI-IC V4.1 は1998年にリリースされ、最終的に 2011年の SATRI-IC UL まで進化しましたが

やはり特性が良くて超えることは超難題でした。残念ではありますが、とはいえ SCCM-LE および SCCM-ME それぞれ成果はあったと感じます。

まあ小手先であれば進歩した部品の採用、ローノイズトランジスタ、マッチドペアのデュアルトランジスタ、

表面実装コンデンサのモジュール搭載などの手段はありますし、自分で設計してみるのはアリだと思いました。