![]() 記事作成中 Under construction

記事作成中 Under construction

サブプロジェクトについて

はじめに

本サブプロジェクトは、高電圧で動作する静電型ヘッドホン用アンプ回路を設計・製作します。高電圧アンプの技術検証を目的としています。

背景・目的

STAX製イヤースピーカー (コンデンサ型ヘッドフォン)向けに、簡易構成の 静電型ヘッドホン用アンプ 「 自作ドライバ :SSDRV」を試作することにしましたが、

設計すべきものがとても多いためプロジェクトを細分化しました。

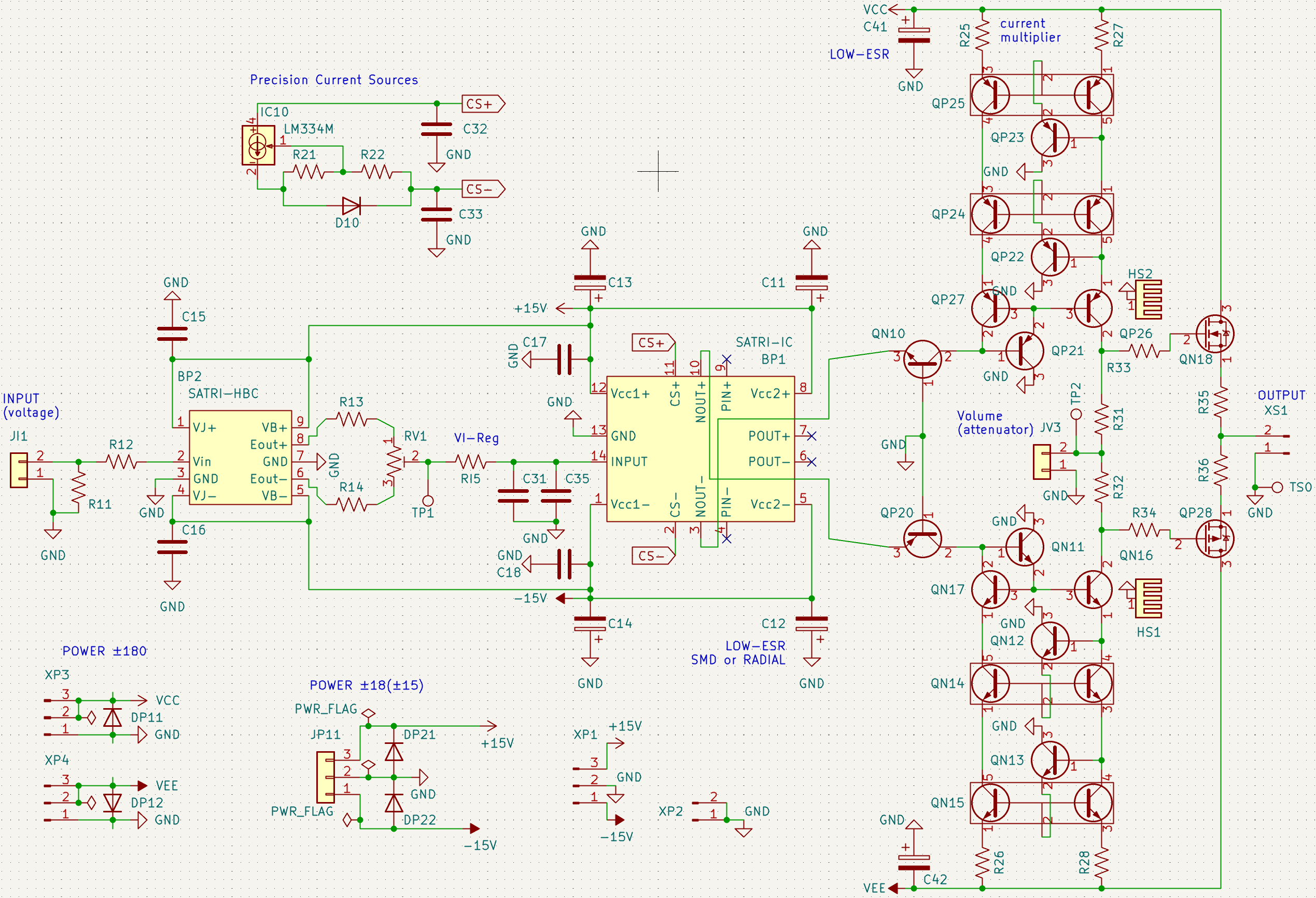

SATRI回路技術 ( サトリ回路 ・ SATRIアンプ )の入力増幅段 を生かすこと、および、SATRI回路技術の出力段 を複数種類試すことなどを考慮して、5ブロックに分割することにしました。

- 「SSDRV INPUT」 高電圧アンプ:入力増幅段

- 「SSDRV output TYPE-xx」 高電圧アンプ:出力段

- 「PS2L v1」 電源回路:低電圧・定電圧安定化電源

- 「PS1H-RG v1」 電源回路:高電圧・定電圧安定化電源

- 「PS1H-BC v1」 電源回路:バイアス電圧、兼、高電圧整流平滑

本サブプロジェクトではこのうち入力増幅段、出力段について設計検討を行います。

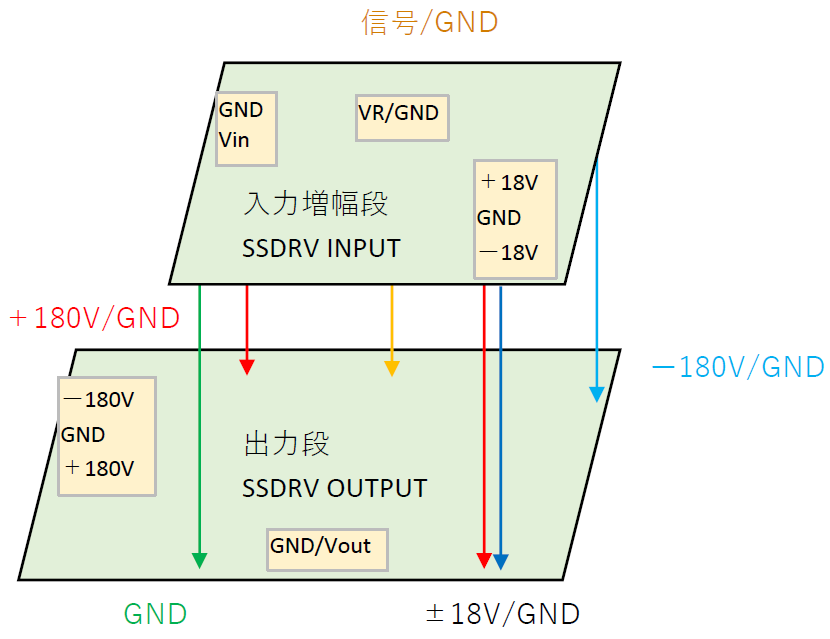

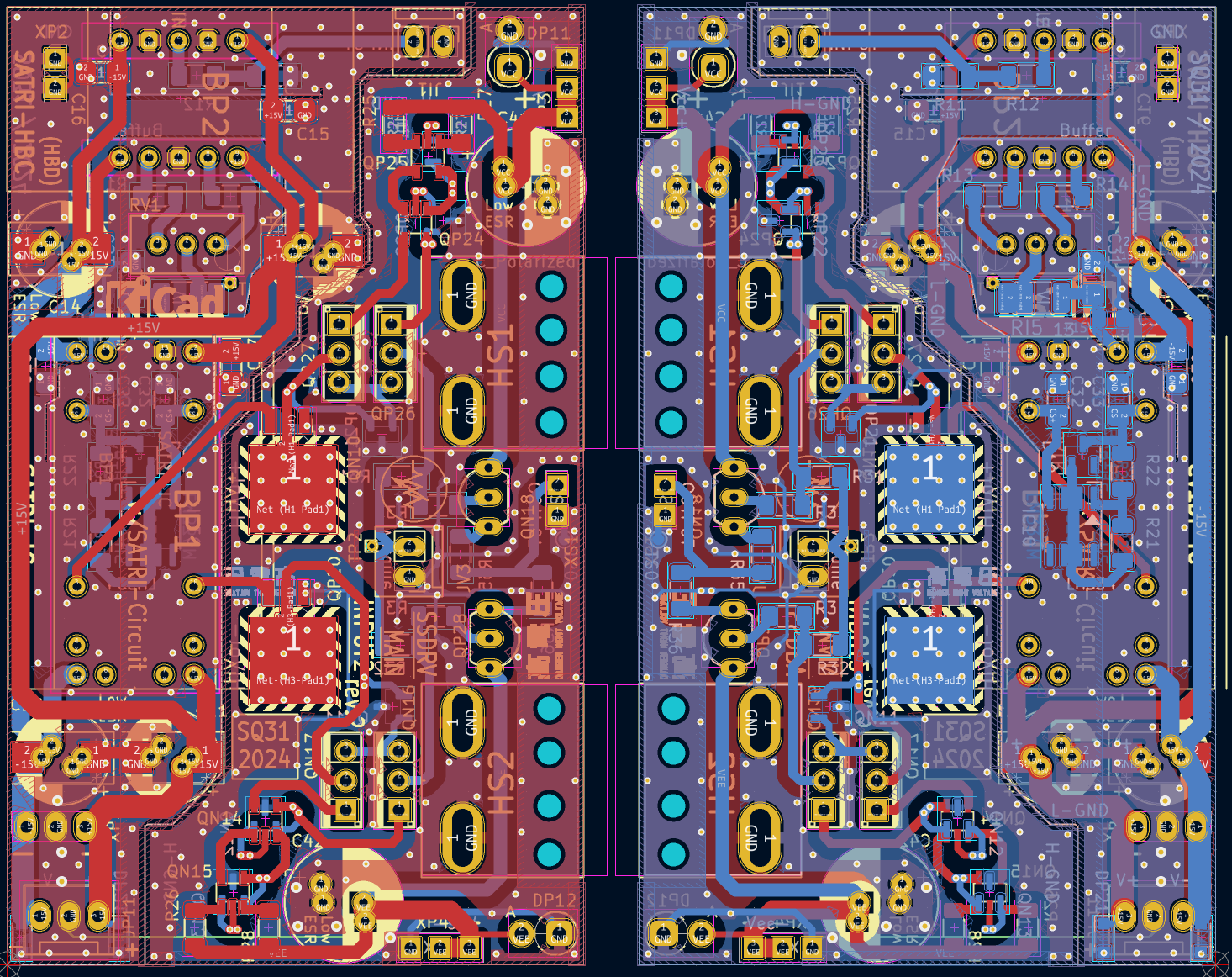

プリント基板構成について

試作版では、入力増幅段(SSDRV input)と出力段(SSDRV output)は基板を分けて積み重ねて利用することとしました。

プリント基板サイズをコンパクトにする目的に加えて、

モジュール化することで上半分・下半分だけ入れ替えることができ部分的な改善作業を行えるようにします。

これまでに入力増幅段 SSDRV INPUT のプリント基板は2種類、出力段 SSDRV output のプリント基板は3種類 設計しています。

どの組合せでも動作しますが最新のものがより改善した回路となっています。

2024年7月時点では、 入力段増幅段 v2「 SSDRV INPUT2」+ 出力段 v3「SSDRV output Type-QGs」の組合せになります。

留意点

- SATRI回路技術を用いた無帰還アンプ回路です。次の特徴があります。

- SATRI回路方式のゲイン調整による音量調整を行います。

- 出力オフセット電圧はバイアスサーボによりキャンセルします。

- 低ESR電解コンデンサを多用しています(ポリマー固体電解コンデンサなど)。

- 表面実装部品を多用しています(コスパ良く精度良好の現行部品を使用)。

- 低電圧の電子工作とは世界が異なる!ということを強く意識する必要があります。

感電事故・負傷を防止するために必要です。

プリント基板はいずれも一発動作しましたが、その後の各種計測中の不注意により複数素子を飛ばしてしまいました。 手元が狂った作業ミスが要因とはいえ、そもそも安全に計測作業ができるようあらかじめ基板デザインで部品配置の配慮や、 計測しやすいテストポイントを盛り込んでおくことが重要だと理解しました。

(仕事で作業するときは当然作業手順書を事前用意していますが) 趣味であっても簡単な作業手順メモを事前に用意することで作業トラブルを軽減できます。 - 固体電解コンデンサを多用しているので本領発揮まで数十時間の通電が必要です。 部品メーカー(旧:佐賀三洋工業、現:パナソニックインダストリー社)の技術資料にも ハンダ付け後に本領発揮するまで100時間程度必要というような記載があります。特に通電開始後の数時間は激変するため出音を即判断しないでください。

- 工具については、別ページ「工具について」にまとめました。

コンポーネント:SSDRV INPUT2 (高電圧アンプ入力増幅段 v2)

概要

『 SSDRV INPUT2 』は高電圧アンプの前半分、入力回路および増幅回路になります。

後述の出力回路 SSDRV output と組み合わせて使います。

作業時期は詳細設計開始 2023年10月、音出し 2024年2月です。前半部のプリント基板は2枚目であり 入力増幅段 v2 です。

以前に製作していた『SSDRV INPUT v1』(設計着手2023年1月、音出し2023年5月)というものがあったのですが、

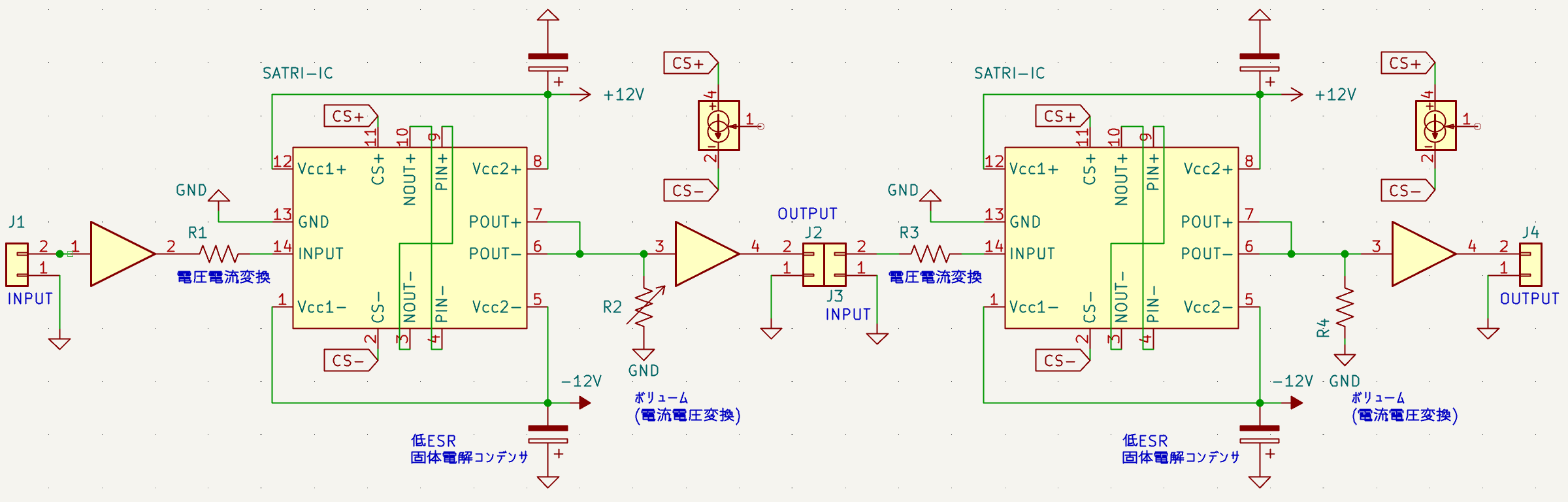

「外付けプリアンプ」+「入力増幅段」+「出力段」の3回路構成となっていました。

この外付けプリアンプは既存の「XLRバランスプリアンプ v1」を利用していたのですが、

これだと「電圧・電流・電圧・電流・電圧(VIーIVーVIーIV)」変換をすることになります。

簡素化すると次のようなイメージで、前半分がプリアンプ、後ろ半分が高電圧アンプ相当です。

プロジェクト初期段階は仕方ない面もあり、高電圧アンプを実現するためには 手持ちのものを活用して、新しく設計・製作するものを簡素化して難易度を下げることが必要でした。 しかしそれにしても「SSDRV INPUT v1」は音の経路が複雑と言えます。 またプリアンプにて音量調整(※上記回路のR2)していたので、 「入力増幅段」は固定ゲインとなりそこに高抵抗(※上記回路のR4)をつかって電流電圧変換(IV変換)している問題がありました。 高い抵抗(※R4)はS/Nの低下につながるので使わずに済ませたいと思っていました。

本サブプロジェクトでは、回路規模が大きくなりすぎた前半2回路「プリアンプ+入力増幅段」をまとめて「SSDRV INPUT2」として

高電圧アンプの入力増幅段を再設計します。

これなら SATRI回路方式アンプの利点 である 小音量~普段利用音量におけるS/Nを向上させることが可能 となります。

実際に使用する音量において比較的低いIV変換抵抗値 (5kΩ以下)に抑えることができます。

そもそも音の経路をシンプルにして回路を単純化することで音の鮮度が上がるのではないか?とも思いました。

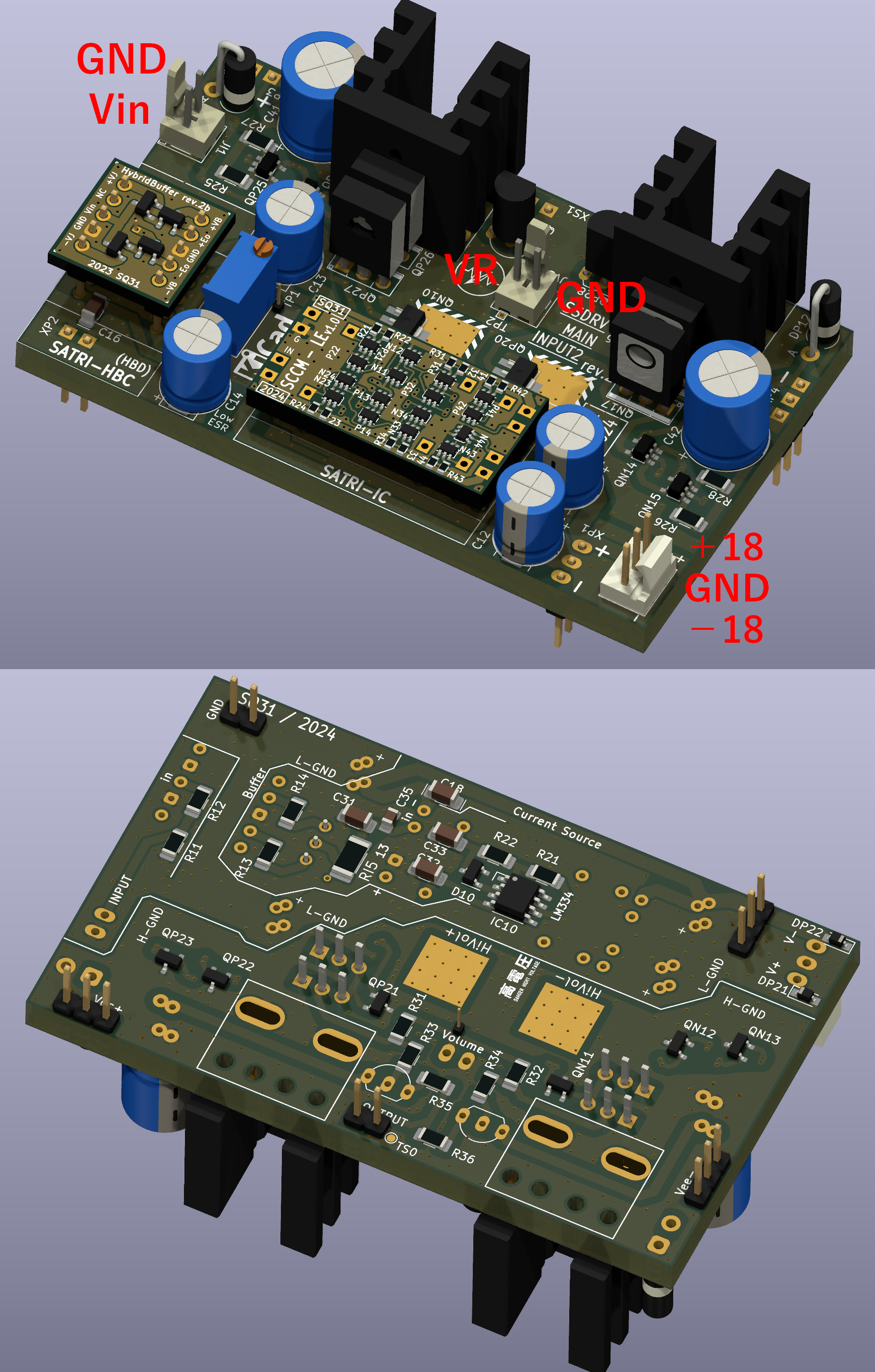

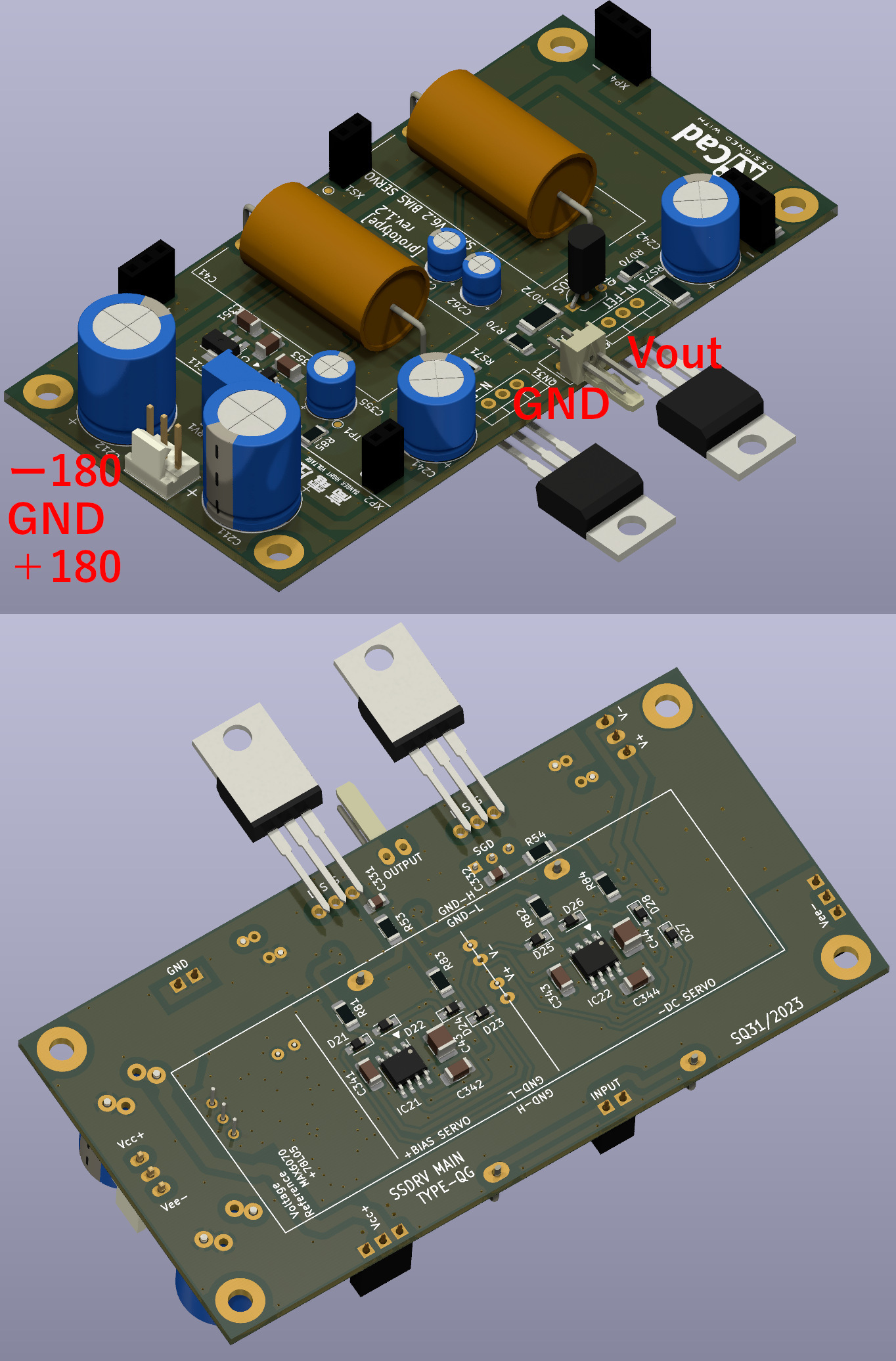

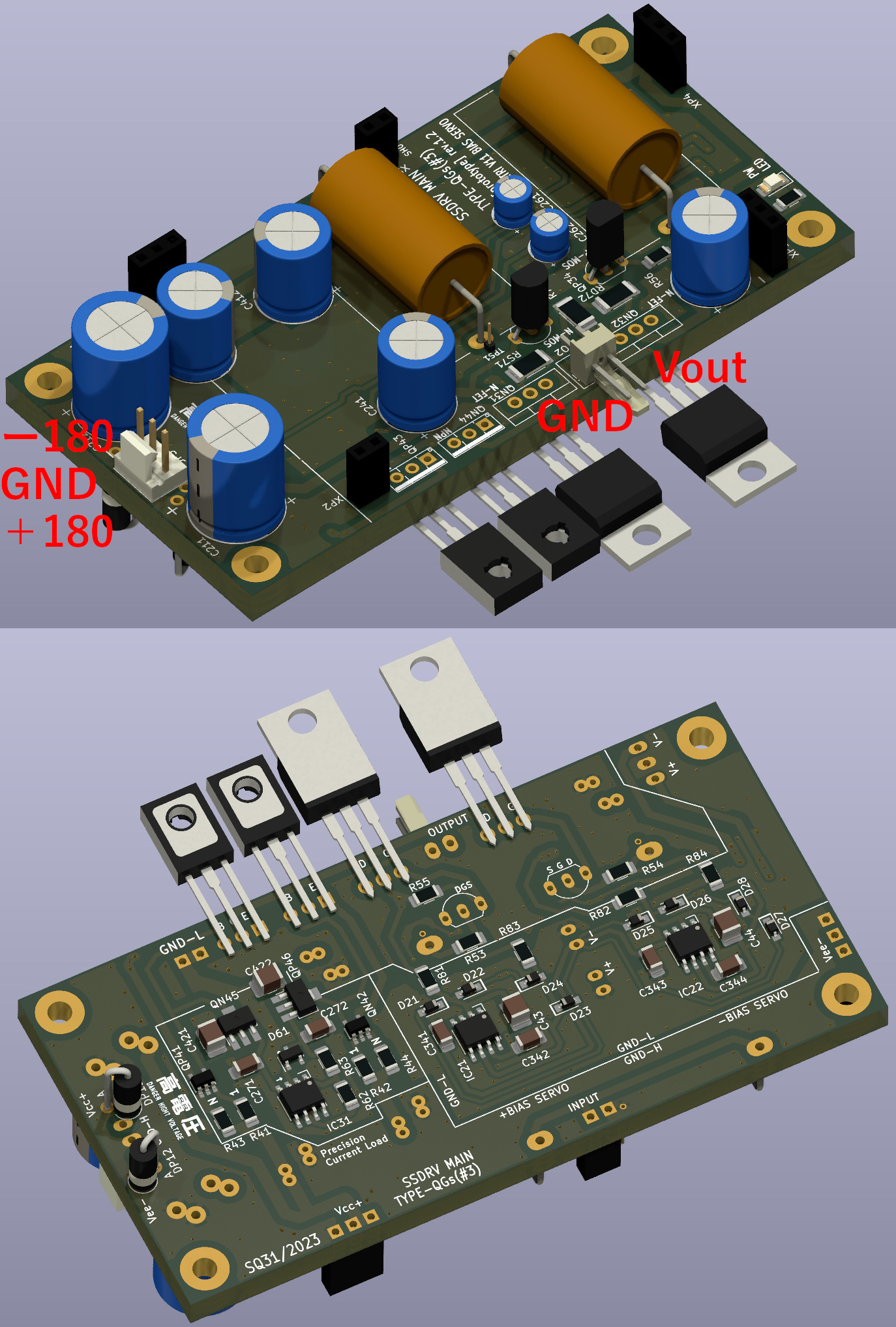

写真

SSDRV INPUT2 全体の写真です。

入力増幅段は(出力段プリント基板の)上に乗せる子基板のため足がついています。

ヒートシンクは 高精度カレントミラー用 の 高耐圧バイポーラトランジスタ が2個ねじ止めされています。

電源電圧±180Vともなると数mAでも損失が大きくなり放熱対処が要るようになります。

設計

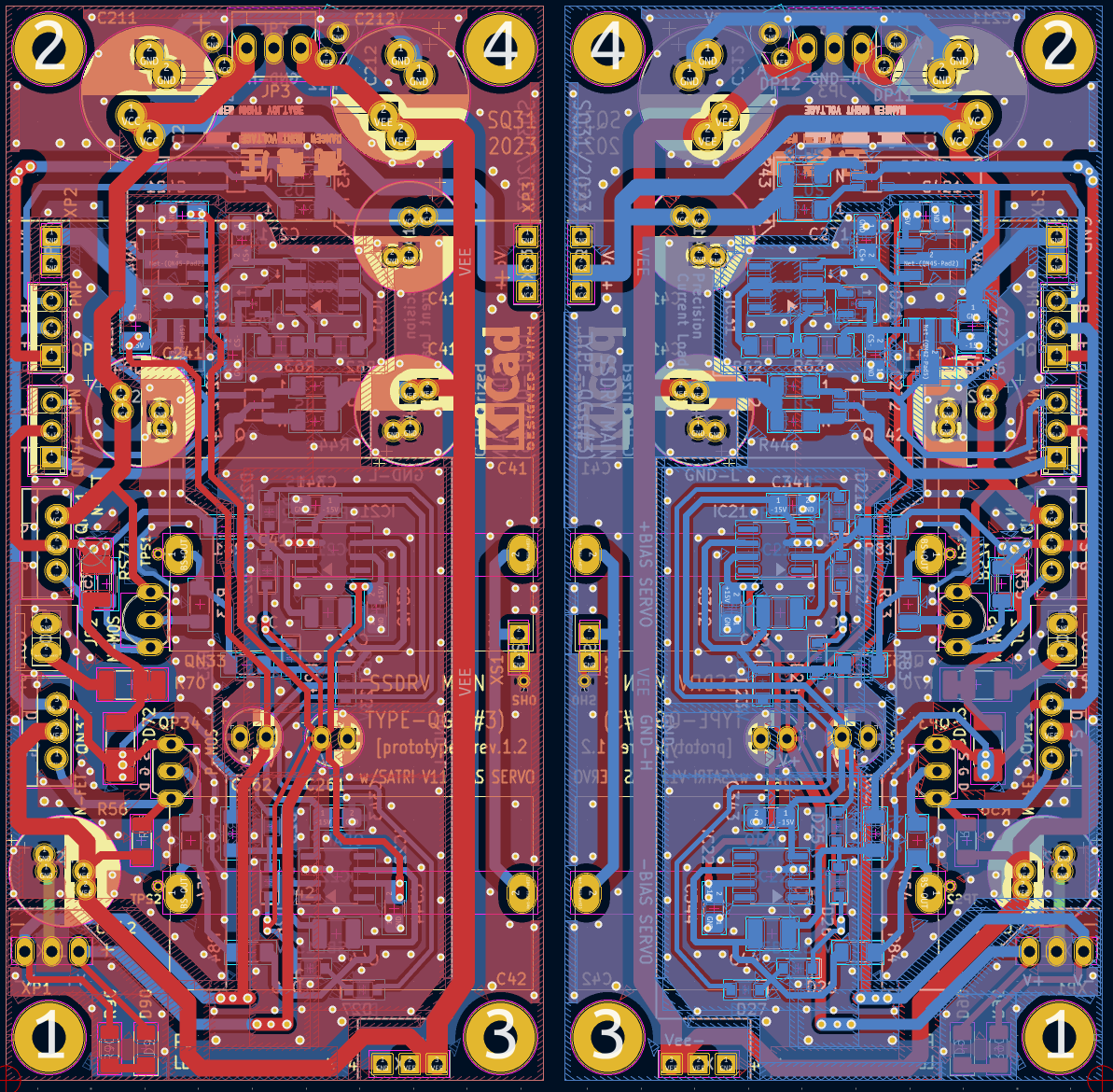

プリント基板は2層(表・裏)です。

高電圧と低電圧の回路が同居していますが、高い電圧側はプリント基板のクリアランスも広くなっています。GNDは高電圧と低電圧で分離しています。

低電圧回路と高電圧回路の間にあるレベルシフトBJT(ベース接地)もそこそこ発熱しますが、パターンで放熱するようにしています。

調整方法

SSDRV INPUT2基板にはオフセット調整用の可変抵抗RV1があります。 入力バッファのオフセット電圧を極小化することでハイブリッドICに入力する信号を適切にします。 オフセット調整は次のように行います。

- 入力をGNDとショートして、入力0Vとします

- 入力バッファHBDを使用している場合は、先にHBDを0V調整しておきます

- 次にTP1を0mVに近づくように前方の可変抵抗RV1を調整します。

出力段にはバイアスサーボがあることから出力オフセット自体は常に抑えられているのですが、 とはいえアンプの各段階が想定通り動作するように適切に調整していた方が良いです。

計測・テスト

テストをするためには、 「高電圧アンプ:入力増幅段 (SSDRV INPUT)」、「高電圧アンプ:出力段 (SSDRV output)」、 「低電圧電源 (PS2L v1)」、 「高電圧電源 (PS1H-RG v1 + PS1H-BC v1)」 を全てそろえる必要があります。

電源回路のテストがおわったら、とりあえず1回路だけ高電圧アンプ親子基板を接続して先行テストすることとします。

もちろん通電するときには絶縁手袋をして、腕も露出しないように長袖の服を着て行いました。

最小単位でテストを重ねていき、万一壊したときの被害を最小限に抑えることに留意して確認作業を進めます。

とにかく石橋を叩いて渡ることを心がけます。

高電圧アンプの特性や安定性も分かってないので恐る恐る調べていくことにします。

高電圧アンプについては、数秒間、瞬間的に電源オンにして異常ないか確認したり、

入力0V(入力とGNDをショート)にて出力にオフセットが出ていないか安全性を順次確認します。

2枚のプリント基板(入力増幅段 + 出力段)の各箇所、入力増幅段の出力なども想定通りの電圧かを丁寧に見ていきます。

発熱についても重要であり、許容損失考慮して設計しているとはいえ異常発熱が無いかも確認します。

そのあと10分以上通電させて安定性・安全性も確認していきます。

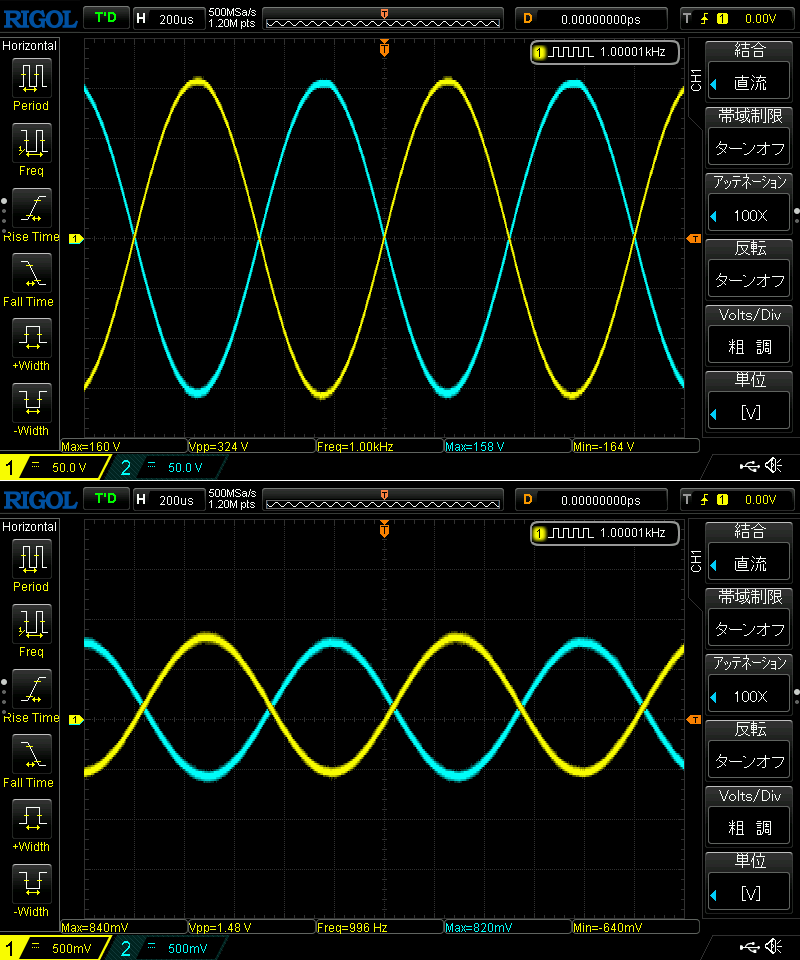

オシロスコープの高電圧プローブで測定した実波形の例です。

波形:左上はXLRバランス入力のHOT/COLDについて2基板の出力をそれぞれ計測したときのもの、

波形:左下は1回路分の入力増幅段と出力段の出口にて計測したときのものですが、

振幅の大小が ±150V ~ ±1.5V であり静電型ヘッドホン用アンプならではの波形だと思います。

このときの設計では最大ボリューム(100kΩ)で243倍なので47dB位ですが、

スタック社製品がおおむね増幅度60dBなのと比べると控え目です。

まあSATRI回路方式なら必要があれば電流電圧変換抵抗(IV抵抗)を大きくすることで対応可能です。

波形:右上は、XLRバランス入力において、ボリュームを更に上げてHOT/COLDの出力サイン波がクリップした様子です。

使用した高電圧の半導体の多くが400V耐圧品ということもあり、電源電圧は±180V以下で設計しておりこれは仕方ありません。

とはいえ±50Vも出せばどのイヤースピーカーでもうるさい位なので、個人的には実用上は問題無いと思っています。

なおボリュームで高ゲイン考慮しているのは小音量ソース(機器・音源)などのために必要があるためです。

波形:右下はXLRバランス入力にて音楽信号を入力した例で、HOT/COLDにて出力できて胸をなでおろしました。

テスト入力信号のサイン波の発生にはPC用の信号発生ソフトを使っています。efuさん作の WaveGene というソフトです。

2024年9月からweb archiveではなく本家からダウンロード可能となっています。

https://efu.sub.jp/soft/wg/wg.html

PCサウンド機能を使うことになるのですが、 きっちりテスト信号出すなら廉価品でいいのでDTM入門機とかのオーディオインターフェイスが良さそうです。

設計補足、部品留意点、製造留意点

- SATRI回路の 高精度カレントミラー は発振しやすく、電源インピーダンスを下げるために

バックアップコンデンサ ・ デカップリングコンデンサ(パスコン) として 低ESRの固体電解コンデンサ が必要不可欠です。

以前は精々100V耐圧品しかなくてブリーダー抵抗でコンデンサを直列にして使う案しかなく、実装上の制限がいろいろある状況でした。 近年登場した 高耐圧の固体電解コンデンサ (高耐圧ポリマーコンデンサ) KEMET A759 の250V品のおかげで設計簡略化できて大変助かりました。 - 電流電圧変換抵抗(IV抵抗)について信号電圧が200V級ともなると、薄膜チップ抵抗だと電力定格0.2Wくらいであり定格電力オーバーとなってしまいます。 かといって音質では世間評判がよろしくない厚膜チップ抵抗は定格1.0W品があるとはいえ正直使いたくありません。 「マイコン制御ボリューム」についても音質面で定評がある表面実装抵抗の中で1W品をなんとか探しまして、高音質のボリュームを実現することができています。

- そのほかの抵抗については、コストパフォーマンスと音質から薄膜チップ抵抗を推奨しておきます。 逆に厚膜チップ(メタルグレーズ厚膜抵抗)は音質面から個人的には非推奨です。 ネット自作記事を探すと音質比較評価などもありますので、まずはコスパよい品で試してみることを強く推奨します。

- SATRI-IC (ハイブリッドIC)は耐圧定格が±30Vなのですが、

これはハイブリッドIC内にて小型表面実装BJTをつかっていて電源電圧や許容損失など制限があることに起因しています。

そこで外付けの折り返しカレントミラーを用意して、レベルシフトBJT(ベース接地)を介して高電圧の電流出力を実現します。

今回の 外付けカレントミラーについては3段重ねになっていて(カスコードカレントミラー)、 更にベース電流補償型の複雑なカレントミラーになっています。 これは SATRI V9回路 と呼ばれる超高精度に電流コピーを実現するカレントミラー回路になります。 ちなみに3段カスコードのうち高電圧がかかるのは1段であるため残り2段は耐圧が低いデュアルBJTを利用することも検討可能です。 - 折り返し外付けカレントミラーには電流が結構ながれてしまうこともあり、 高耐圧にするとともに許容損失・放熱についても十分考慮する必要がありました。 (電流半減させてIV抵抗値を倍にする等で)放熱を押さえる案もあったのですが、ヒートシンクをつけてでも音質優先にて設計しました(高抵抗を使わないようにしました)。

- 電流電圧変換抵抗(IV抵抗)のあとにはバッファを用意して、出力段をスムーズに駆動できるように回路構成しています。 ここでJFETでは高耐圧品が無いし(※SiC-JFET除く)、 バイポーラトランジスタだと駆動電流が必要になってしまうことから用途的に向いて無くて、 MOS-FETしか選択肢としてありません。 このMOS-FETの400V耐圧のうちCissが小さいもので探すと、Microchip社の小信号MOSFETが丁度いいスペックでした。 エンハンスメントMOSFETなので抵抗をつかった簡易バイアス回路としています。 (初期のSATRI-AMP製品で使われていた回路案です。SATRI-ICのOUT+/OUT-にはバイアス電流が乗っているので可能です)

- 入力増幅段の出力端子(回路図 XS1)では出力電圧波形にオフセット電圧が数V乗ることがありますが問題ありません。 これは入力増幅段のDCサーボ回路を省略しているため仕方がありません。 ただ出力段にはカップリングコンデンサがあり実用上は問題ありません。 (ただし数十ボルトのオフセットが乗るときは、製造不良や半導体破損の可能性があるので即調査します)

- ハイブリッドICの発振防止でC31、C32、C33が必要です(C35は予備で未使用)。 個人的には小音量時に発振した事例があったので 1000pF にしています。

- 発振したときの対処法としては、予備C35にコンデンサを実装する案、ゲート入力抵抗(R12、R33、R34)を1kΩなどに増やす案、 予備パスコン(C15、C16、C17、C18)にMLCC等のコンデンサを追加する案もあります。

コンポーネント:SSDRV output Type-QG (高電圧アンプ出力段 v2)

概要

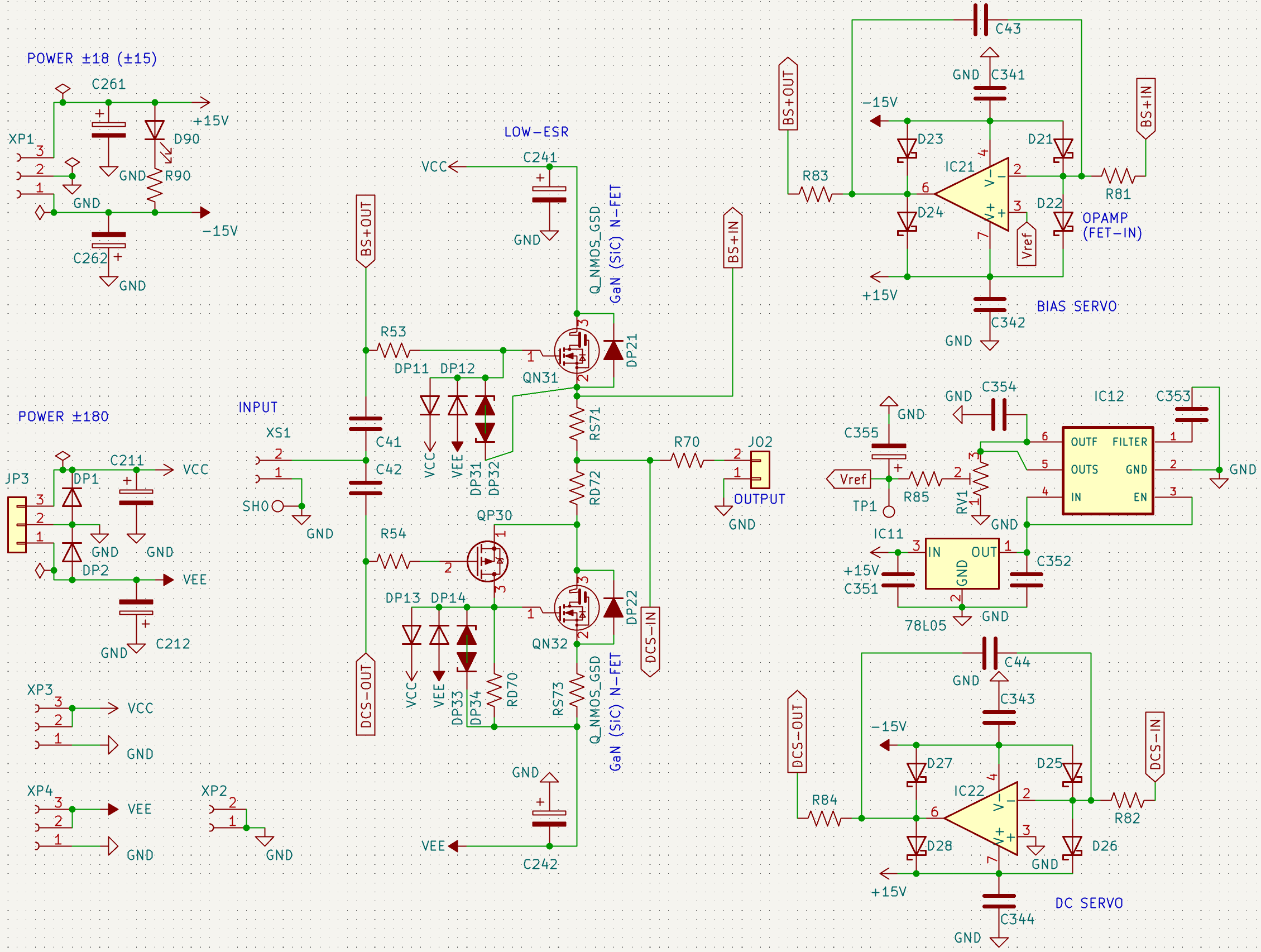

『 SSDRV output Type-QG 』は高電圧アンプの後ろ半分、出力回路になります。SATRI回路方式「V6.2バイアスサーボ」を使用しています。

前述の入力増幅回路 SSDRV INPUT と組み合わせて使います。

作業時期は詳細設計開始 2023年1月、プリント基板発注 2023年3月末、音出し 2023年5月です。

後半部のプリント基板は2枚目であり 出力段 v2 です。

GaN-FET (ガリウムナイトライド)の音を聴いてみたい!!

静電型ヘッドホン用アンプつくるなら高耐圧 GaN がピッタリではないか!、正直なところ素子ありきで設計着手しています。

長年、音の評判が良い最新世代の半導体素子を試してみたい!と強く思っていました。

SiC-FET はそこまででもなかったのですが GaN は惹かれました。

ただネット上のGaN自作記事みると誰もが素子を何度も飛ばしているということで相当じゃじゃ馬だと理解しました。

となると比較的扱いやすそうなGaNとしては、Nexperia社

あるいは transphorm社 の

カスコード型 GaN FET(Si-MOSFET & GAN-HEMT)のTO-247・TO-220パッケージ品が現実的と考えました。

その中でCissが比較的小さくドライブしやすそうということ、

とにもかくにも値段も中では一番安いというのもありTP65H150G4PS を採用することとしました。

本サブプロジェクトでは 高電圧アンプの出力段 を設計します。

ここでGaN FETはNch品しかないので出力回路としては 準コンプリメンタリ となります。

なお SiC FET は音響的評判が微妙であるような記事を多数みかけたため比較評価の採用は見送りました。

写真

SSDRV output Type-QG 全体の写真です。

子基板の入力増幅段を取り付けるソケットがあり、親基板・子基板を連結して利用します。

入力増幅段の信号をそのまま出力するバッファ回路になっています。

出力段の基板サイズは統一しているのでプリント基板には比較的余裕があります。

基板裏面にはBIASサーボとDCサーボ、基板表面には高精度電圧リファレンスあたりが少し込み入っている程度です。

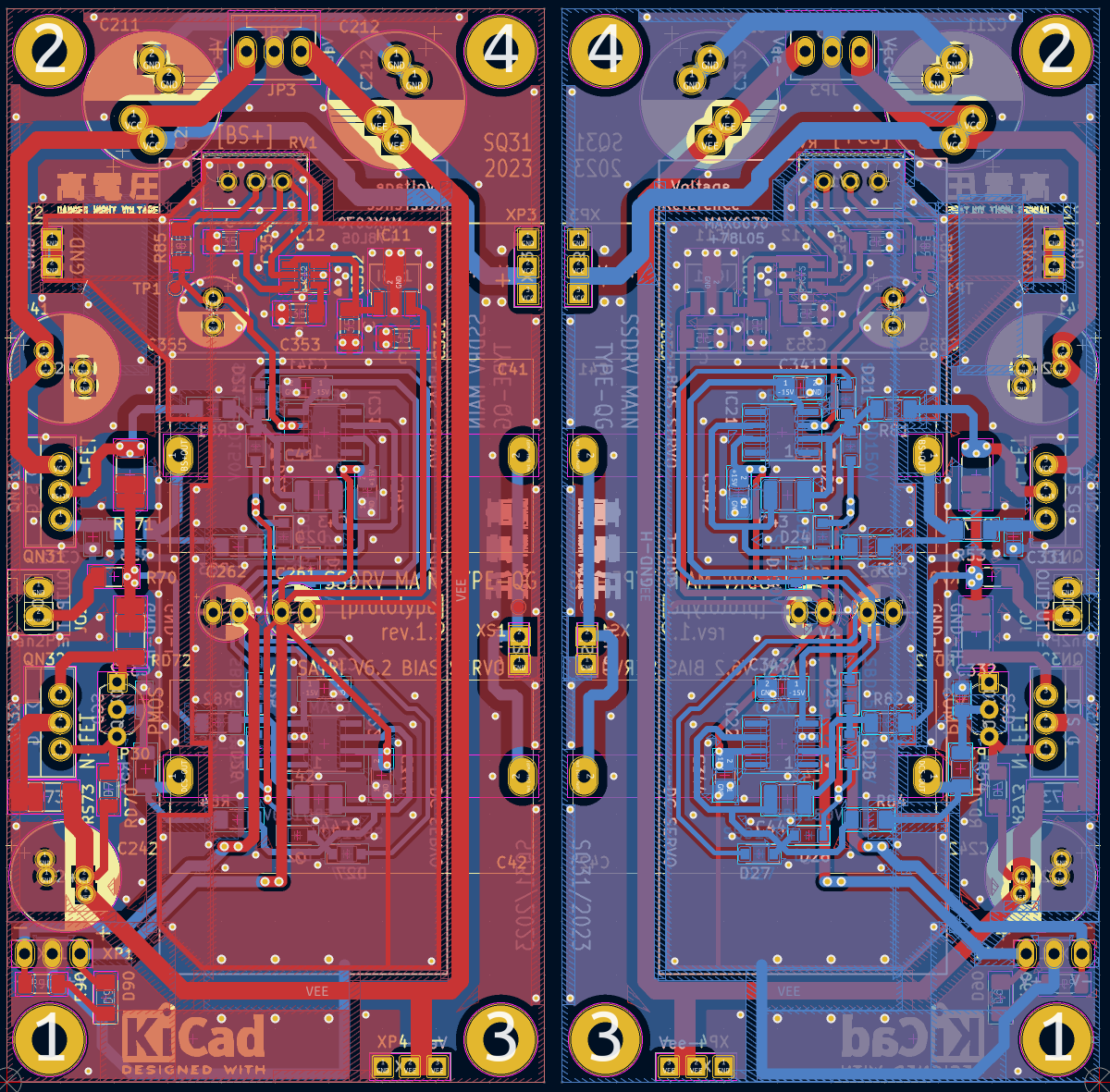

設計

プリント基板は2層(表・裏)です。

高電圧と低電圧の回路が同居していますが、高い電圧側はプリント基板のクリアランスも広くなっています。

GNDは高電圧と低電圧で分離しています。

回路検討:保護回路について

GaNアナログアンプはネット上の複数作例において安定性に難あるという記載を見かけており プロジェクトでは慎重に作業を進めていましたが、 (計測や製造の不注意破損を除き)自分もGaN FETを2回飛ばしています。 GaNでは放熱不足の熱暴走のほか、電源オンオフなどに発生したと思われるサージ電圧(?)にて破損した感触もありました。 破損すると上下GaN-FETに異常貫通電流が流れるのかソース抵抗も一緒に損傷します。 電源電圧±180V級だと周辺回路道連れにするため出力基板ごと作り直しになることが数回ありました。

そこで故障率を下げるべく保護回路についても検討しました。

発熱についてはバイアス電流抑える等で対処するとして、

それでも異様に破損しやすいGaN-FETについてはサージ電圧などの過電圧保護(ゲート入力保護)の追加を行いました。

未だに損傷する詳細発生メカニズムは分かっていませんが、下記の保護回路追加により以降は抑止できていると感じています。

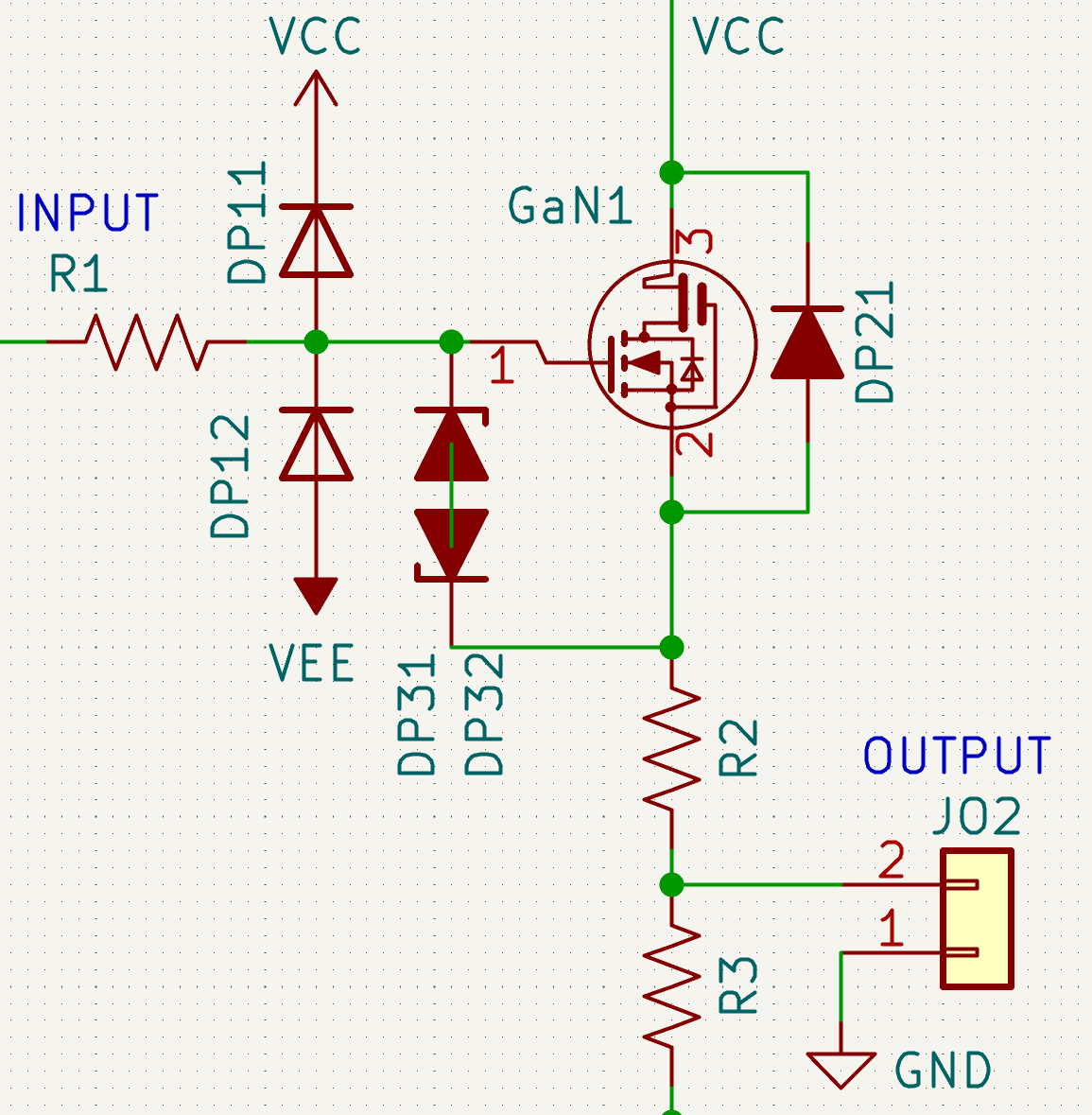

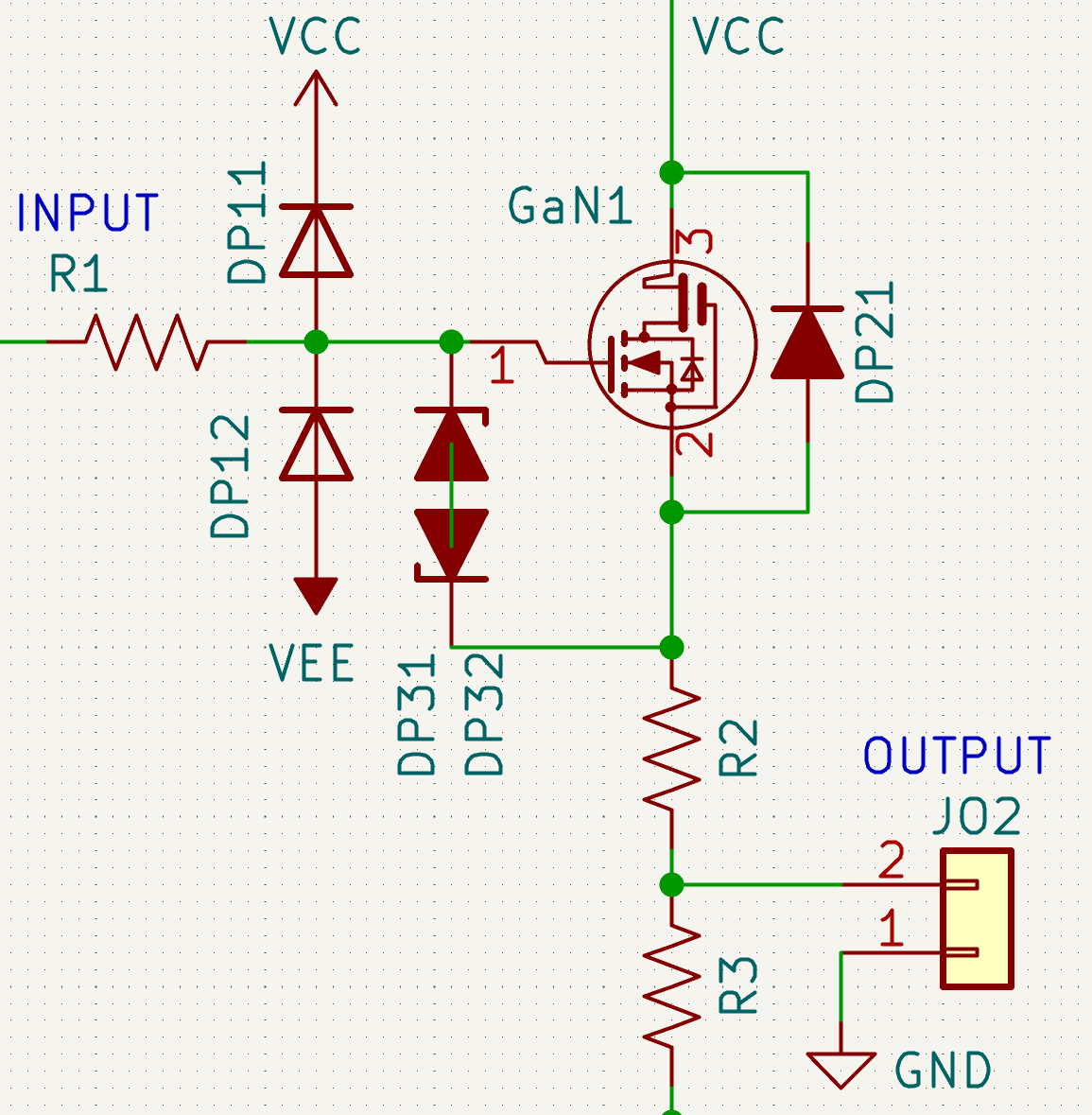

- 従来

(下図)MOS-FETのゲート抵抗R1、ソース抵抗R2くらいでした。なお静電型ヘッドホンのインピーダンスが約145kΩ大きい事もあり、 静電型ヘッドホン用アンプではソース抵抗を数十Ω~百数十Ωなど大きくすることが出来ます。 - GaN-FET保護

(1)Vgs制限の ツェナーダイオード DP31・DP32、および、 (2)ゲート入力保護( クランプダイオード )DP11・DP12 などが効果があると想定しています。 なお (3)サージ電圧吸収 : ボディダイオード相当 DP21 については MOS-FETにあってGaN-FETに無いということで追加しましたが、正直なところ効果は不明です。

(ネット上の文献を調べると、スイッチング電源の保護回路ではこれら外付けダイオードが使われており、GaN FET利用においても必須だったのかもしれません。勉強不足でした)

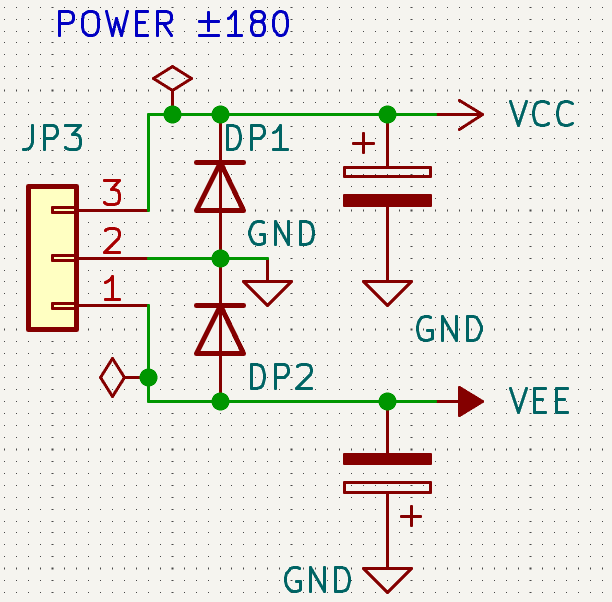

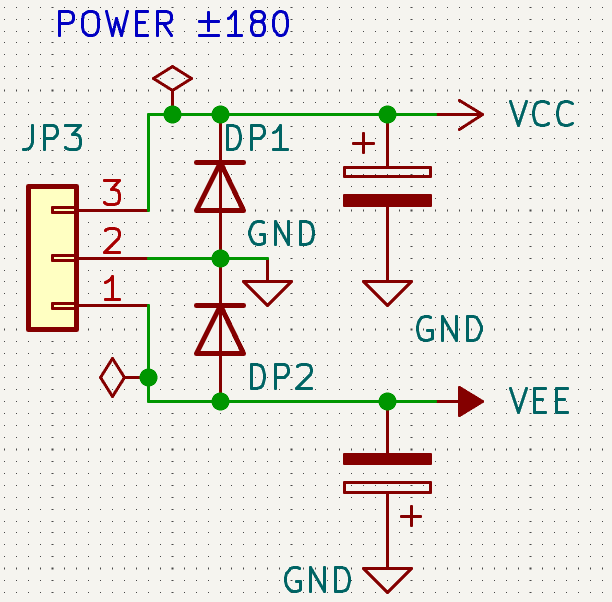

- 電源異常電圧保護

出力GaN FET損傷や電源系トラブルなどにより異常電源電圧がかかるとドライバの上基板・下基板がともに破損してしまいます(1回経験あり)。 少しでも低減させるべく電源コネクタ近くに異常電圧軽減の保護ダイオード DP1・DP2 を追加検討しました。 なおこのとき(電源トランス1次側)電源ヒューズを飛ばすことでの保護を想定しているので適切なヒューズ選定が必要です。 (保持電流が大き過ぎると切れないし、小さすぎると電源オンの突入電流が溶断電流を上回ります)

- 電源突入電流保護

電源オンのときの突入電流防止ですが本サブプロジェクトでは未実装です。 ソリッドステート・タイマ(リレー)を使うと簡単に構成できますが、リレーとディスクリートの遅延オン回路でも組んだ実績があります。 今後必要があれば用意することとします。

- 出力の過電流保護回路

出力FET過電流保護についてはネット上の自作記事ではGaN FET破損防止にうまくつながった事例がみつかっておらず検討保留としています。

なお静電型ヘッドホン用アンプでは出力保護・感電防止の高抵抗(R70)があるので、実際には一部保護は組み込まれています。しかしGaN-FETの破損防止としての効果はない状況です。

GaN FETの出音は大変気に入っていますが、安心して使い続けるにはまだまだ保護回路の改善が必要と思っています。

とはいえまずはこのまま年単位で安定性を見てみたいと考えています。

調整方法

SATRI V6.2回路 は、上に バイアスサーボ があり基準電圧を調整するとバイアス電流が決まります。

GaNの熱暴走による素子破損は絶対に避ける必要があり、

十分に放熱できていない場合(放熱板を長い間触ってられない熱さの場合)、

可変抵抗RV1を調整してバイアスを低く抑えて発熱低減させます。

悩ましいのは極少量に絞るよりは多少流した方が好ましい出音になることです(スルーレート影響?)。安全に倒しつつも多少流すバイアス塩梅は難しいと思います。

具体的な調整方法としては、電源投入前に調整用の可変抵抗RV1は最小にしておきます(RV1の 1:GND ~ 2:摺動部 を最小値にする)。

テスターで設定電圧TP1を計りつつ徐々に大きくして設計値まで上げつつ、

ヒートシンクが適切に放熱できていることを確認するようにします。

なおバイアス設定値は「ソース抵抗RS71値 × 設定バイアス電流 = TP1設定電圧」で計算しますが、当初はバイアス 5mA ~ 10mA で様子をみることとしました。

※GaNが飛ぶとソース・ドレイン導通して周辺回路もろとも損傷します。 損傷個所を特定できずSSDRV output基板1枚を作り直しとなることがあります。 後悔しないよう高いバイアス電流で攻めず、バイアスを多少抑えた安全側で使用しましょう。

計測・テスト

オシロスコープの高電圧プローブにて順次計測を行っていきます。

高電圧アンプについては、数秒間、瞬間的に電源オンにして異常ないか確認したり、

入力0V(入力とGNDをショート)にて出力にオフセットが出ていないか安全性を順次確認します。

その後、基板の各箇所が想定通りの電圧となっているか丁寧に確認していきます。

波形:左はXLRバランス入力のHOT/COLDについて2基板の出力をそれぞれ計測したときのものです。

電圧が高いので最初に計測するときは毎回緊張します。

バイアスサーボ回路によりオフセット電圧は常に抑えられています。

波形:右上は電源オン直後のサーボ挙動(黄色:BIASサーボ、水色:DCサーボ)。波形:右下は電源オフ直後のサーボ挙動(同)です。

オペアンプの電源電圧±18Vに余裕をもって収まっています。

そのあとGaN-FETを放熱板で十分放熱できているかもしっかり確認します。

もし放熱板を手で長い間触っていられない熱さだとGaNが飛ぶかもしれないのでバイアスを下げるようにします。

また10分以上通電させて安定性・安全性も確認していきます。

設計補足、部品留意点、製造留意点

- 準コンプリメンタリ を実現するため、Pch MOS-FET を使っています。 上下の対称性が高くないように感じますが、簡単に作れるというので本構成としました。

- 高耐圧ポリマー固体電解コンデンサ については入力増幅段同様に採用します。 電源インピーダンスを下げる デカップリングコンデンサ(パスコン)・バックアップコンデンサ として優れています。 とはいえ高耐圧品だと価格面も考慮すると 2.2uF~8.2uF程度と出力段としては少ない容量です。 通常の 液体電解質 の 低ESR電解コンデンサ を電源コネクタ接続部にバックアップコンデンサとして用意することで対処しています。

- SATRI V6.2回路 は、基準電圧をもとにしてバイアスサーボがかかります。 このバイアス精度向上のため基準電圧がブレないように 高精度電圧リファレンスIC をつかっています。 リファレンスICのデータシートを参考にして、IC近くにMLCC(C0G特性)を直近に配置しています。 なおリファレンスICは入力電圧の制限があるので3端子レギュレータで5Vを作っています。

- バイアスサーボ回路 では入力に カップリングコンデンサ が必要になり、容量1.0uFですが高耐圧品が必要となりますので、 スピーカネットワーク用フィルムコンデンサ (メタライズドポリプロピレン)で探しました。 デンマーク Jantzen Audio の Standard-Z シリーズは廉価な割にまとまりよく、 中低域の音が前に出てくるタイプでウーファー用ネットワークに自分も以前から使っています。 ただ聴き易い音である反面、低域が若干過剰となりボワつく要因になっているかもしれません。難しいです。 他の選択肢、米ASC は購入経路が見つからず未採用、独 mundorf社 EVO系は高額だしと、 なかなか選定できずにいます。

- サーボ用オペアンプは、当初は高耐圧のバイポーラとMOSFETとで高耐圧ディスクリート品を作る予定でした。

ただLTSPICEシミュレーション結果から、音楽信号であれば入出力保護ダイオードをつければ実用上は問題なさそうだと

判断して一般的な電源電圧±18V対応のオペアンプ(JFET入力)で構成することとしました。

とりあえずの検証用としては廉価品 TI TL071HIDR にしました。

他の選択肢としてはプリアンプで用いた TI OPA1655などもありますが高価なこともあり、 検証中に破壊する可能性も高いため避けました。 なおオペアンプ保護ダイオードはFRD品ではなく推奨の高速SBD品にしましたが、 小型表面実装SBDだと耐圧が150V位までしかなくあまりよろしくない使い方です(実用上はそんな電圧かからないとはいえ)

感想・反省点・今後の課題

魅惑の音とでもいいますか、心地よくてずっと聴いていたくなります。 GaN-FET は、なんというか柔らかく温かみある音っぽく感じるも、解像度高めの中高域はクールな透明感ある独特な音がします。

GaN-FETの出音は大変満足しましたが、満足したからこそ新しい回路技術を適用した音を聴いてみたいと強く思うようになりました。

今回の回路技術 V6.2バイアスサーボ よりも新しい技術にて出力段を再設計します(後述 Type-QGs)。

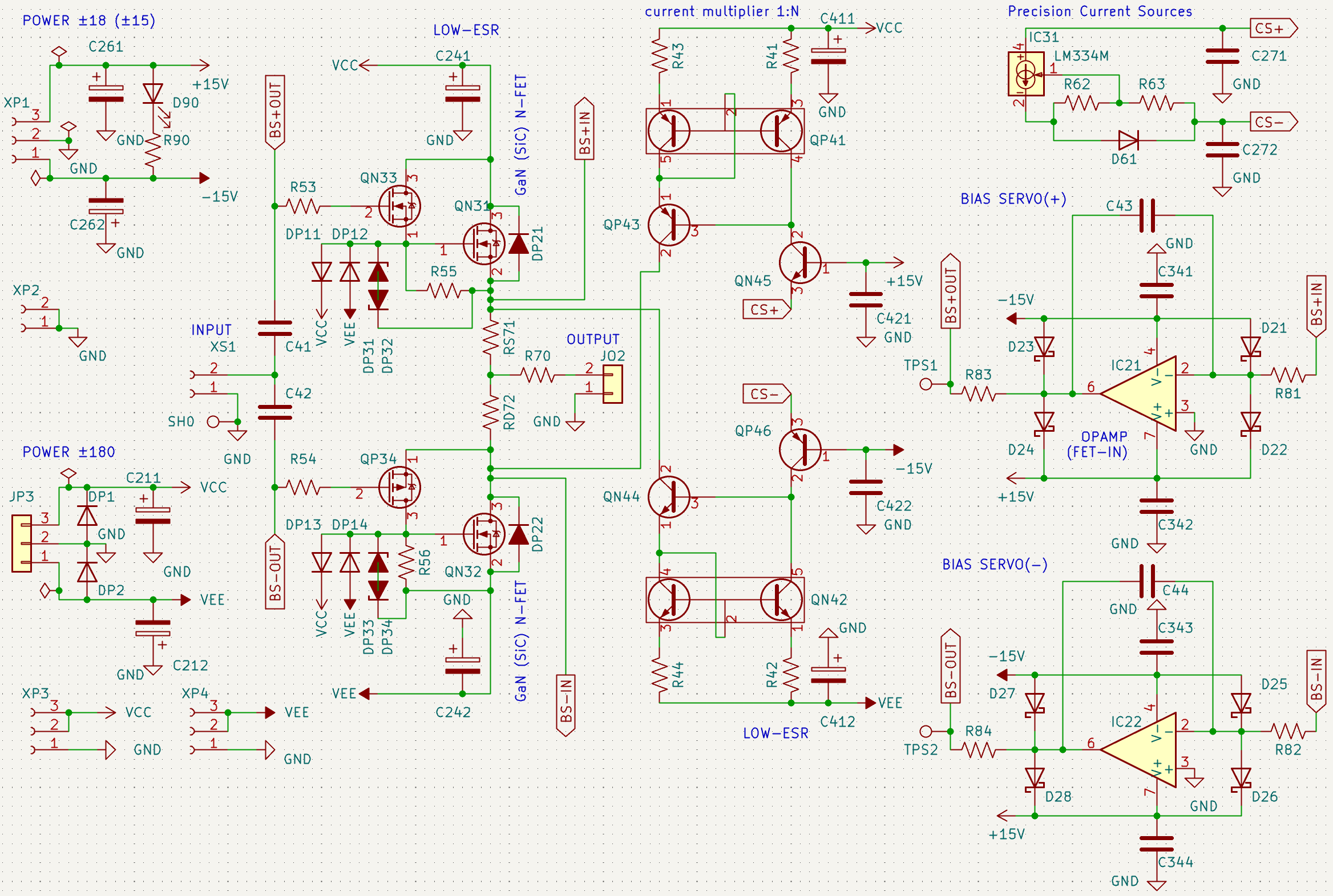

コンポーネント:SSDRV output Type-QGs (高電圧アンプ出力段 v3)

概要

『 SSDRV output Type-QGs 』は高電圧アンプの後ろ半分、出力回路になります。

前述 Type-QG の改善版であり、SATRI回路方式「V11.xバイアスサーボ」を使用しています。

入力増幅回路 SSDRV INPUT と組み合わせて使います。

作業時期は詳細設計開始 2023年7月、音出し 2023年9月です。

後半部のプリント基板は3枚目であり 出力段 v3 です。

GaN-FET出力段「SSDRV output Type-QG」の出音は大変満足しました。

柔らかく温かみある音っぽく感じるも解像度高めの中高域は透明感ある独特の音がします。魅惑の音とでもいいますか、心地よくてずっと聴いていたくなります。

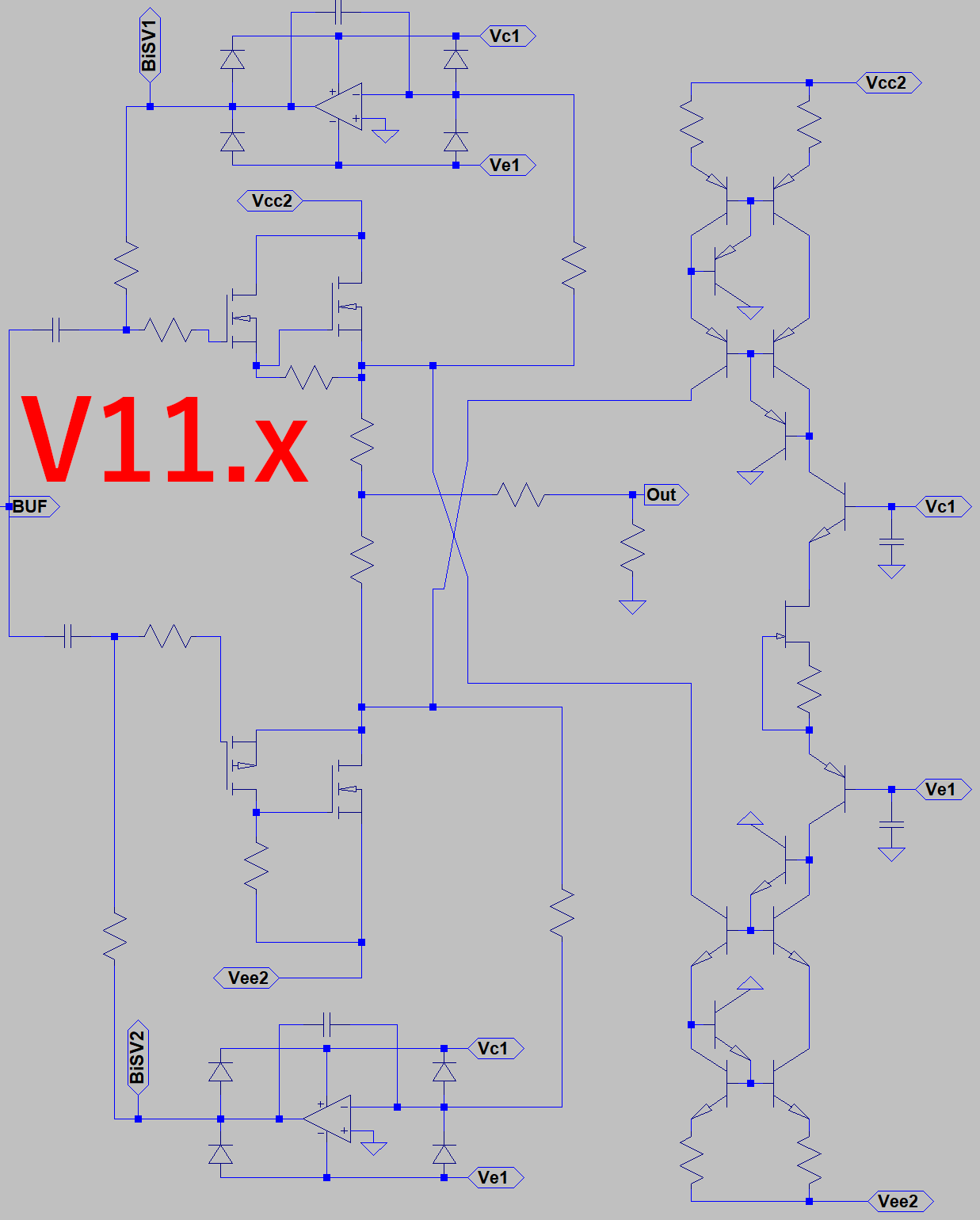

しかし使用しているSATRI回路技術はV6.2(BIASサーボ + DCサーボ)というもので、

出力段の精度向上のためサーボ回路にてバイアスを固定化しますが2003年の古い技術でした。

その後2009年にV11.x (V11.1~V11.4)という後継バイアスサーボ回路が出ており、

更なる高精度化を狙って設計された回路でした。

更なる音質向上につながるのならと、静電型ヘッドホン用アンプ出力段としてV11.x回路の検討だけは細々続けていました。

具体的にはLTspiceを用いてシミュレーションを行っていました。

検討当初は逆に歪率が大きく悪化してしまいましたが、色々検討を重ねて良好な結果を得ることができました。

本サブプロジェクトでは、V11.x回路を元にしたGaN-FET準コンプリメンタリ出力段を改めて設計することとします。

写真

SSDRV output Type-QGs 全体の写真です。

子基板の入力増幅段を取り付けるソケットがあり、親基板・子基板を連結して利用します。

入力増幅段の信号をそのまま出力するバッファ回路になっています。

出力用GaN-FET、定電流源のBJT、バイアスサーボ OPAMPx2、LM334 など結構苦労して詰め込んだプリント基板になっています。

設計

V11.x バイアスサーボ回路 では定電流負荷でバイアスを引いており、 出力(ソース抵抗)には音声信号のみとしてバイアス電流を流さないことで精度向上を狙った回路になっています。 V11.1等 では SATRI V9回路方式 の 高精度カレントミラー が使われているのですが、定電流源として用いると高精度電流コピーが逆効果のようでした。 結果に違和感がありLTspiceで1kHz~96kHzのサイン波を入力して隅々まで調べると分かってきました。

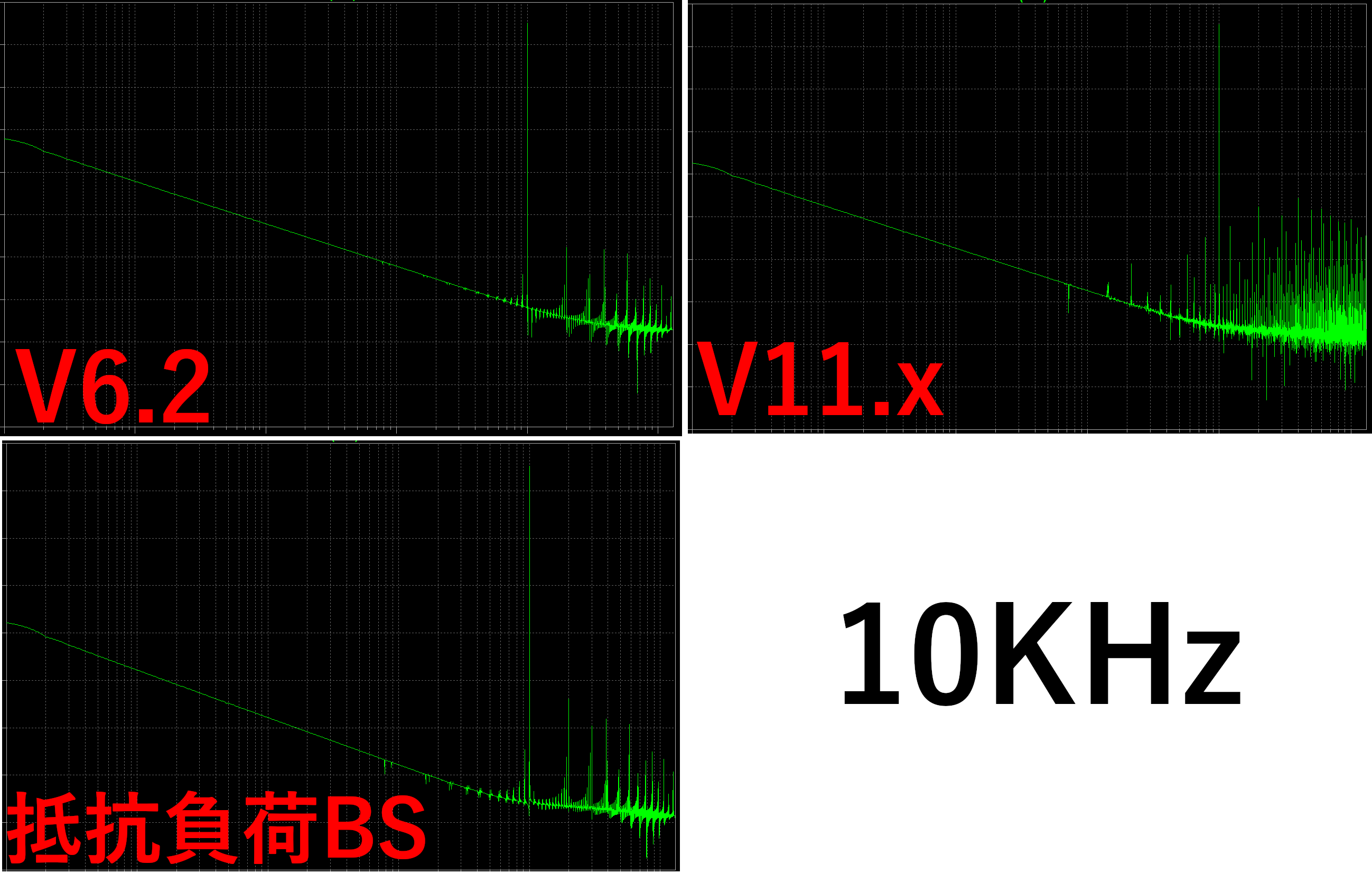

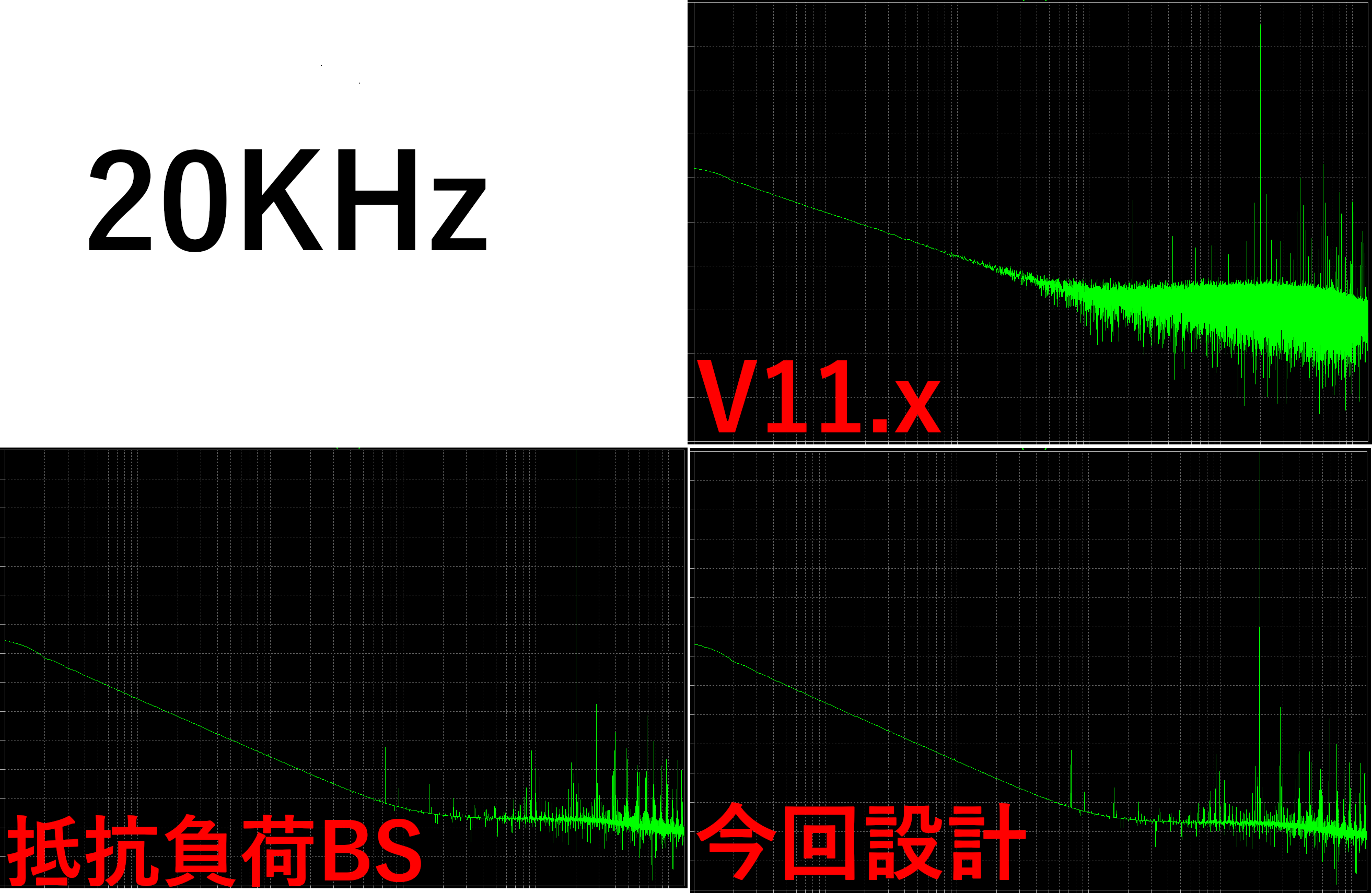

10kHzサイン波入力のときの出力電圧FFTみるとV11.xと比べて、(2020年の最新版)抵抗負荷バイアスサーボ回路方式 の方が優れているように感じます。

なおV6.2は前製作「SSDRV output Type-QG」の回路(バイアスサーボ + DCサーボ)です。

抵抗負荷バイアスサーボ は後述「SSDRV output Type-CF」の回路です。

20kHzサイン波入力のときの出力電圧FFTみるとV11.xは顕著に更に悪くなっていますが、今回設計した簡素化した電流源(ウイルソンカレントミラー利用)だと

(抵抗負荷バイアスサーボと)いい勝負だと思いますし、

バイポーラトランジスタ利用もあって出力インピーダンスが高いよりよい電流源負荷にすることができています。

保護回路は「SSDRV output Type-QG」と同様です。

GaN-FET保護(ゲート保護)、電源異常電圧保護 を行っています。

プリント基板は2層(表・裏)です。

高電圧と低電圧の回路が同居していますが、高い電圧側はプリント基板のクリアランスも広くなっています。

GNDは高電圧と低電圧で分離しています。

計測・テスト

オシロスコープの高電圧プローブにて順次計測を行っていきます。

高電圧アンプについては、数秒間、瞬間的に電源オンにして異常ないか確認したり、

入力0V(入力とGNDをショート)にて出力にオフセットが出ていないか安全性を順次確認します。

その後、基板の各箇所が想定通りの電圧となっているか丁寧に確認していきます。

波形:左上および波形:左下は、XLRバランス入力のHOT/COLDについて2基板の出力をそれぞれ計測したときのものです。

振幅の大小が ±160V ~ ±0.8V となっており静電型ヘッドホン用アンプならではの波形です。

バイアスサーボ回路によりオフセット電圧は常に抑えられています。

波形:右上は電源オン直後のBIASサーボ挙動(黄色:上側、水色:下側)。波形:右下は電源オフ直後のBIASサーボ挙動(同)です。

オペアンプの電源電圧±18Vに余裕をもって収まっています。

前回Type-QG と 今回Type-QGsとはサーボ方式が細々異なるので、サーボのかかり方も異なります。

あと発熱量が2倍となりかなり凄いので放熱板で十分放熱できているか、長時間通電しても放熱は問題無いか念を入れて確認します。

もし放熱板を手で長い間触っていられない熱さだとGaNが飛ぶかもしれません。素直にバイアスを減らしましょう。

調整方法、設計補足、部品留意点、製造留意点

- SATRI V11.x系回路 はバイアスを定電流源で引くという構成のため消費電力は SATRI V6.2回路 の2倍になります。 もちろん発熱も増えるので放熱も大変になります。そういうデメリットがあっても音質追求したいということであれば検討する余地があります

- バイアスサーボは上下のバイアス電流を一定に保つよう制御がかかります。 なおサーボ電圧自体は高電圧ではないので、 サーボの入力と出力の過電圧保護用ダイオード(SBD)を付けることで一般のJFET入力オペアンプを使うことができます。

- (前製作output Type-QGから見直し)GaN-FETの準コンプリメンタリ回路について対称性を近づけるため上側にも駆動用Nch MOS-FETを追加しています。

- 出力段のバイアス電流は抵抗比 R41:R43 および R42:R44 で決まりますが、調整のためには抵抗交換が必要です。

具体的に R43=R41ならLM334設定電流そのままのバイアス電流となり、たとえば R43を1/3にすれば LM334設定電流の3倍のバイアス電流となります。

なおR42・R44も同じ値に合わせます。

当初はバイアス 4mA ~ 8mA で様子をみることとしましたが、 (出力段v2 の V6.2サーボ回路 と比較すると2倍の発熱量もあり)GaN-FET放熱に十分注意してあまり上げすぎないように留意します。 そのこともあり設定用抵抗 R43・R44 については複数回路定数を用意しておくことを推奨します。

コンポーネント:【没】SSDRV output Type-CF (高電圧アンプ出力段 v1)

概要

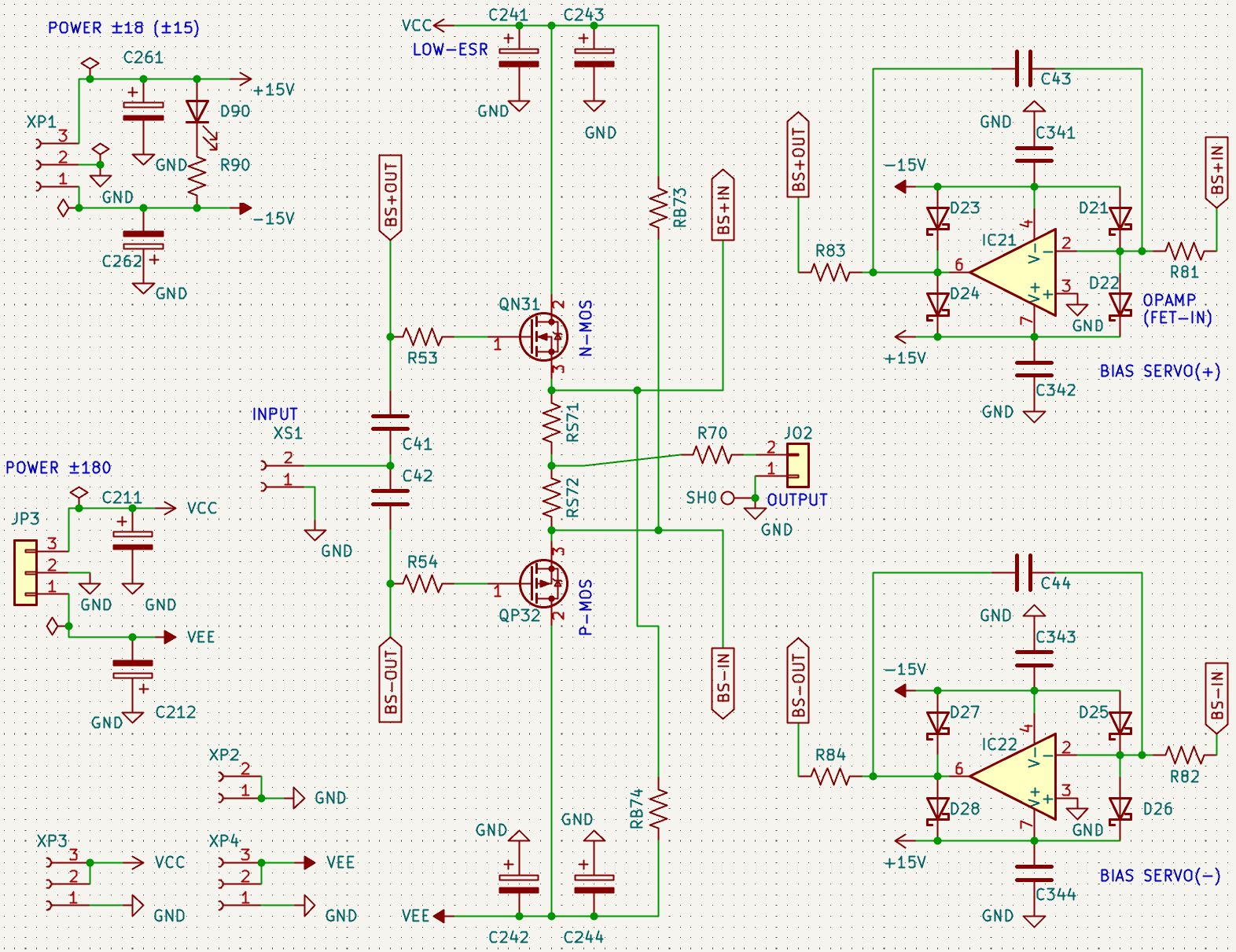

『 SSDRV output Type-CF 』は高電圧アンプの後ろ半分、出力回路になります。SATRI回路方式「抵抗負荷バイアスサーボ」を使用します。

前述の入力増幅回路 SSDRV INPUT と組み合わせて使います。

作業時期は詳細設計開始 2023年1月、プリント基板発注 2023年3月末、音出し 2023年5月です。

実は「output Type-QG」は出力段v2基板、 「output Type-QGs」は出力段v3基板であり、 その前にこの「output Type-CF」 出力段v1基板がありました。 一番最初に設計した出力段v1は Pch MOSFET と Nch MOSFET を組み合わせたコンプリメンタリ仕様のものです。 とはいえ市場にはペアとして売られている高耐圧Pch MOSFETはなさそうなので、同一メーカーの近い製品を組み合わせて作ることになります。

ここで出力素子Pch MOSFETの選択肢が現行品だと殆どありませんでした。

vishay siliconix社 だと IRFU310PBF/IRFU9310PBF。

onsemi社 だと FQP5N60C/FQP3P50 および後継品でしょうか。

個人的には(旧)三洋半導体 の希少な 2SK2403/2SJ458 を持っていたのですが、

ディスコン品で新規設計するのは極力避けたかったため使用していません。

本サブプロジェクトでは、IRFU310PBF/IRFU9310PBF の Pch/Nch MOSFET をつかった出力段を設計することとしていました。

初めて音が出た瞬間は感動しましたが、しかし早々にお蔵入りしてしまいました。 ぶっちゃけて言うと眠い音といいますか、出音が自分の好みではありませんでした。 GaN-FET (output Type-QG(Type-QGs))の透明感あるクリアな響きを聞いてしまうとMOSFETを選択する気になりませんでした。

ただ出力段では唯一、出力素子が損傷していません(作業ミス除く)。やはりMOS-FETで作ると頑丈に作れるのだと感じました。

写真

SSDRV output Type-CF 全体の写真です。

写真左、子基板の入力増幅段を取り付けるソケットがあり、親基板・子基板を連結して利用します。

入力増幅段の信号をそのまま出力するバッファ回路になっています。

基板裏面に(バイアスサーボ)負荷抵抗のパワーレジスタ(5W(7W))が取り付けられています。

写真右は手持ちのディスコン半導体。市場在庫も枯渇したものは新規設計では控えるべきということで採用見送りました。

設計

プリント基板は2層(表・裏)です。

高電圧と低電圧の回路が同居していますが、高い電圧側はプリント基板のクリアランスも広くなっています。

GNDは高電圧と低電圧で分離しています。

設計補足、部品留意点、製造留意点

- 出力段v1 回路は 2020年の最新版「 抵抗負荷バイアスサーボ回路方式 」を参考にしています。

実はこの後に作る 出力段v2 回路は 2003年の「 V6.2回路 バイアスサーボ 」、 また 出力段v3 回路は 2009年の「 v11.x バイアスサーボ 」となっています。 サトリ回路世代でいえば 出力段v1 が新しい世代となっています。

一応、抵抗負荷バイアスサーボ方式にて GaN-FET準コンプリ回路 は 設計実現できるのですが採用せず見送っております。 - 本回路(output Type-CF)はバイアスを抵抗負荷で引くという構成のため、消費電力は SATRI V6.2回路(output Type-QG) の約2倍になります。

そういうデメリットがあっても音質追求したいということであれば検討する余地があります。

(抵抗負荷式(Type-CF) も V11式(Type-QGs) もバイアス電流の影響を低減させますが、

抵抗負荷式はシンプルに構成できる利点、V11式はより理想的な電流源とすることができる利点があり、一長一短あります。

なお V6.2式(Type-QG)は調整しやすい利点があります)

抵抗負荷は電力定格が大きいパワーレジスター(5W や 7W 品など)を使います。 定格に十分余裕をもたせて選定したのですが手で触れないほど熱くなり少し心配になります。 - 出力段のバイアス電流は抵抗負荷 RB73・RB74 で設定します。

バイアス設定値は「電源電圧(正) ÷ 抵抗負荷RB73 = 設定バイアス電流」で計算しますが、

当初はバイアス 6mA ~ 12mA で様子をみることとしました。なおRB74も同じ設定値にします。

出力段のバイアス電流の調整は抵抗負荷 RB73・RB74 の交換となりますが、 パワーレジスター(5W や 7W 品)となると抵抗E12系列(12k、15k、18k、22k、27k、33k、39k、47k)から選定することになると思っておいた方がよいです。 バランス4回路となると計8個必要となることもあり数多くの回路定数を事前用意することも難しく、調整しつつの比較試聴が困難でした。 なおパワーレジスターは基板にがっちり固定されていて交換が大変という点も比較試聴に向いていません。

サブプロジェクト中止

2024年11月下旬、静電型ヘッドホン用アンプの運用終了して技術検証作業は終了しました。本サブプロジェクトも終了します。

正直に言えばGaN運用断念しました。素人の自分にはGaN-FETアナログアンプの安定稼働は無理だったようです。

出力段「SSDRV output Type-QGs」は14ヶ月目で再破損しました (「SSDRV output Type-QG」含めると18ヶ月のGaN運用)。 新しい保護回路も効果不十分だったのかもしれませんし他の要因かもしれません。 故障基板を再作成せず断念するのは、故障の原因究明をすることが出来ず再破損否定できない為です。

自作ドライバは諦めていませんが、とはいえ稚拙な初期設計に基づいた複雑基板というのは再製作作業も結構大変なこともあり、 大幅に簡素化しつつ回路も抜本的に見直した部品サブプロジェクトを新たに始めたいと思います。

GaN-FET独特の透明感あるクリアな響き大好きだったよ...